Difference between revisions of "CRTC"

(→Links) |

|||

| (798 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

| − | + | [[File:CRTC Type 0.jpg|thumb|right|CRTC Type 0 (Hitachi)]] | |

| + | [[File:CRTC UMC Type 0.png|thumb|right|CRTC Type 0 (UMC)]] | ||

| + | [[File:CRTC Type 1.png|thumb|right|CRTC Type 1]] | ||

| + | [[File:CRTC6845-Type2.jpg|thumb|right|CRTC Type 2]] | ||

| + | The 6845 '''CRTC''' (Cathode Ray Tube Controller) chip was created by Motorola in 1977. It works with the [[Gate Array]] to generate the video signal on the Amstrad CPC. | ||

| − | + | This chip is also used in the [[BBC Micro]], [[Lynx|Camputers Lynx]], [[EG2000 Colour Genie]], [[Sharp X1]], [[MicroBee]], [[Commodore PET]] and the early graphics cards (MDA, Hercules, CGA, Plantronics Colorplus) for [[IBM PC]]. And it is found in some [https://www.msx.org/wiki/Hitachi_HD6845 MSX1 expansions], providing an 80-column text mode. | |

| + | |||

| + | It's important to note that the CRTC chip is primarily designed for character-based displays. It explains why, on the Amstrad CPC, the video memory is organized into a grid of characters rather than a purely linear bitmap. | ||

NOTE: This document describes the functionality in terms of the CPC with its separate CRTC and Gate-Array. The Plus has both integrated into the same IC, but could be considered to have two functional blocks, one for CRTC and one for Gate-Array. In this document the term 'Gate-Array' is used, but this also applies to the ASIC. | NOTE: This document describes the functionality in terms of the CPC with its separate CRTC and Gate-Array. The Plus has both integrated into the same IC, but could be considered to have two functional blocks, one for CRTC and one for Gate-Array. In this document the term 'Gate-Array' is used, but this also applies to the ASIC. | ||

| Line 9: | Line 15: | ||

The 6845 Cathode Ray Tube Controller (CRTC) is a programmable IC used to generate video displays. This IC is used in a variety of computers including the Amstrad CPC, Amstrad CPC+ and KC Compact. | The 6845 Cathode Ray Tube Controller (CRTC) is a programmable IC used to generate video displays. This IC is used in a variety of computers including the Amstrad CPC, Amstrad CPC+ and KC Compact. | ||

| + | |||

| + | The CRTC is a simple chip. It is made up of counters and equality operators, tied by simple logic. All the complexity stems from its multiple independent implementations with their subtle differences. | ||

The CRTC was a common part available from many different manufacturers. During the life of the CPC, Amstrad sourced the CRTC from various manufacturers. | The CRTC was a common part available from many different manufacturers. During the life of the CPC, Amstrad sourced the CRTC from various manufacturers. | ||

| Line 59: | Line 67: | ||

The 6845 is selected when bit 14 of the I/O port address is set to "0". Bit 9 and 8 of the I/O port address define the function to access. The remaining bits can be any value, but it is adviseable to set these to "1" to avoid conflict with other devices in the system. | The 6845 is selected when bit 14 of the I/O port address is set to "0". Bit 9 and 8 of the I/O port address define the function to access. The remaining bits can be any value, but it is adviseable to set these to "1" to avoid conflict with other devices in the system. | ||

| − | The recommended I/O port addresses are | + | The recommended I/O port addresses are: |

| − | {| | + | {| class="wikitable" |

| − | + | ||

|- | |- | ||

| − | + | !I/O port address | |

| + | !/CS (A14) | ||

| + | !R/W (A9) | ||

| + | !RS (A8) | ||

| + | !Function | ||

| + | !Read/Write | ||

|- | |- | ||

| − | |& | + | |&BCxx||0||0||0||Select 6845 register||Write only |

|- | |- | ||

| − | |& | + | |&BDxx||0||0||1||Write to selected internal 6845 register||Write only |

|- | |- | ||

| − | |&BFxx|| | + | |&BExx||0||1||0|| |

| + | * CRTCs 0/2: — | ||

| + | * CRTC 1: Read Status Register | ||

| + | * CRTCs 3/4: Read from selected internal 6845 register | ||

| + | ||Read only | ||

| + | |- | ||

| + | |&BFxx||0||1||1||Read from selected internal 6845 register||Read only | ||

|- | |- | ||

|} | |} | ||

| − | '' | + | The CRTC is not connected to the CPU's RD and WR pins, so it cannot detect the bus's I/O direction. Therefore, executing an IN instruction to the select or write functions causes the CRTC to write the unpredictable data provided by the high-impedance bus to its registers. |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

==Addressing== | ==Addressing== | ||

| − | The | + | The VMA of the [[Gate Array]] is constructed from the CRTC MA and RA signals: |

| − | {| | + | {| class="wikitable" |

| − | + | |- | |

| + | !Video Memory Address | ||

| + | !Signal source | ||

| + | !Signal name | ||

|- | |- | ||

|A15||6845||MA13 | |A15||6845||MA13 | ||

| Line 91: | Line 108: | ||

|A14||6845||MA12 | |A14||6845||MA12 | ||

|- | |- | ||

| − | |A13||6845||RA2 | + | |A13||6845||'''RA2''' |

|- | |- | ||

| − | |A12||6845||RA1 | + | |A12||6845||'''RA1''' |

|- | |- | ||

| − | |A11||6845||RA0 | + | |A11||6845||'''RA0''' |

|- | |- | ||

|A10||6845||MA9 | |A10||6845||MA9 | ||

| Line 121: | Line 138: | ||

|} | |} | ||

| − | CRTC generates the address, Gate | + | CRTC generates the address, Gate Array reads the data and converts it to pixels based on its current graphics mode and palette. |

| − | + | CRTC pins RA3, RA4, MA10, MA11 are not connected on CPC. | |

| − | + | <br> | |

| + | |||

| + | === Overscan bits === | ||

| + | |||

| + | It is possible to use 32KB screen size (used for [[Programming:Overscan|overscan]]) by setting bits 11 and 10 of Register 12 both to 1. Bits MA11 and MA10 of the address generated by the CRTC are not written on the address bus to access video memory; settings both bits to 1 is the only way to cause a carry to bit MA12 when address pass over the end of current video page to change the memory address to the next video page. | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |+ CRTC Display Start Address | ||

| + | |- | ||

| + | ! colspan="8" | Register 12 | ||

| + | ! colspan="8" | Register 13 | ||

| + | |- | ||

| + | ! 15 !! 14 !! 13 !! 12 !! 11 !! 10 !! 9 !! 8 | ||

| + | ! 7 !! 6 !! 5 !! 4 !! 3 !! 2 !! 1 !! 0 | ||

| + | |- | ||

| + | | colspan="2" | Unused | ||

| + | | colspan="2" | Video Page | ||

| + | | colspan="2" | Page Size | ||

| + | | colspan="10" | Start Address (1024 positions) | ||

| + | |} | ||

| + | |||

| + | {| style="white-space: nowrap;" | ||

| + | |- | ||

| + | | | ||

| + | {| class="wikitable" style="margin-right: 32px" | ||

| + | |- | ||

| + | ! Bit 13 !! Bit 12 !! Video Page | ||

| + | |- | ||

| + | | 0 || 0 || 0000 - 3FFF | ||

| + | |- | ||

| + | | 0 || 1 || 4000 - 7FFF | ||

| + | |- | ||

| + | | 1 || 0 || 8000 - BFFF | ||

| + | |- | ||

| + | | 1 || 1 || C000 - FFFF | ||

| + | |} | ||

| + | | | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Bit 11 !! Bit 10 !! Page Size | ||

| + | |- | ||

| + | | 0 || 0 || 16KB | ||

| + | |- | ||

| + | | 0 || 1 || 16KB | ||

| + | |- | ||

| + | | 1 || 0 || 16KB | ||

| + | |- | ||

| + | | 1 || 1 || '''32KB''' | ||

| + | |} | ||

| + | |} | ||

| + | |||

| + | <br> | ||

| + | |||

| + | === Coarse hardware scrolling === | ||

| + | |||

| + | The start address can be manipulated to achieve horizontal and/or vertical hardware scrolling: | ||

| + | |||

| + | *To move right: <code>start_address := start_address + 1</code> | ||

| + | *To move left: <code>start_address := start_address - 1</code> | ||

| + | *To move down: <code>start_address := start_address + R1</code> | ||

| + | *To move up: <code>start_address := start_address - R1</code> | ||

| + | |||

| + | However, it is a position in word (16 bits), not in byte. So, the screen will move two bytes at a time horizontally. Also, the precision will be one CRTC character vertically. | ||

| + | |||

| + | The first game that used R12/R13 for both horizontal and vertical hardware scrolling is [https://www.cpc-power.com/index.php?page=detail&num=1839 Roland on the Ropes], released in 1984. | ||

| + | |||

| + | The following BASIC program demonstrates the coarse scrolling by setting the R12 and R13 registers based on keyboard input: | ||

| + | |||

| + | <pre> | ||

| + | 10 ma%=0 | ||

| + | 20 IF INKEY(1)=0 THEN GOSUB 100 | ||

| + | 30 IF INKEY(2)=0 THEN GOSUB 300 | ||

| + | 40 IF INKEY(8)=0 THEN GOSUB 500 | ||

| + | 50 IF INKEY(0)=0 THEN GOSUB 700 | ||

| + | 60 GOTO 20 | ||

| + | 100 ' right | ||

| + | 110 ma%=ma%+1: GOSUB 900: RETURN | ||

| + | 300 ' down | ||

| + | 310 ma%=ma%+40: GOSUB 900: RETURN | ||

| + | 500 ' left | ||

| + | 510 ma%=ABS(ma%-1): GOSUB 900: RETURN | ||

| + | 700 ' up | ||

| + | 710 ma%=ABS(ma%-40): GOSUB 900: RETURN | ||

| + | 900 ' set R12 and R13 | ||

| + | 910 l%=ma% AND 255: h%=&30 OR ((ma%\256) AND 3) :OUT &BC00,13:OUT &BD00,l%: OUT &BC00,12:OUT &BD00,h% | ||

| + | 930 RETURN | ||

| + | </pre> | ||

| + | |||

| + | Which looks like the following: | ||

| + | |||

| + | [[File:CRTC-Coarse-scroll.gif]] | ||

| + | |||

| + | <br> | ||

| + | |||

| + | === Advanced hardware scrolling === | ||

| + | |||

| + | To achieve smoother hardware scrolling, other tricks are required in complement to R12/R13. Usually, R3 is used for smooth horizontal scroll and R5 for smooth vertical scroll. | ||

| + | |||

| + | A good example of smooth hardware multidirectional scrolling game on CPC is [https://www.cpc-power.com/index.php?page=detail&num=2119 Super Cauldron], released in 1993. | ||

| + | |||

| + | Everything you need to know about hardware scrolling on CPC can be found [https://www.cpcwiki.eu/forum/programming/hardware-scrolling-21687/ there]. | ||

| + | |||

| + | <br> | ||

| + | |||

| + | == Split screen (aka Rupture) == | ||

| + | |||

| + | While there is usually 1 CRTC frame per screen frame, the screen frame can be divided into multiple CRTC frames of varying proportions. | ||

| + | |||

| + | This is useful for defining different scrolling zones in your screen frame. For example, it was used for hardware parallax scrolling in the game [https://www.cpc-power.com/index.php?page=detail&num=1307 The Living Daylights], released in 1987. [https://www.cpcwiki.eu/forum/programming/the-living-daylights-extra-colours-in-mode-1-rasters-screen-splits/ Source] | ||

| + | |||

| + | And this is basically the bread and butter of innumerable CPC demos. | ||

| + | |||

| + | Some rules of thumb [https://www.cpcwiki.eu/forum/programming/advice-on-split-screen-code/msg242186/ Source]: | ||

| + | * changes to the screen address have to be done anywhere in the previous split | ||

| + | * changes to the height of the split have to be done inside the current split (after it has started, in the area of the size of the previous split) | ||

| + | * changes to screen mode and colours are happening immediately | ||

| + | |||

| + | CRTC registers and screen splitting: | ||

| + | *reg 0 (63) = x-screenwidth (usually always 63) | ||

| + | *reg 1 (50) = x-splitwidth (e.g.50) | ||

| + | *reg 2 (51) = x-splitstart (e.g. 51) | ||

| + | *reg 3 (08) = x-finestart (maybe use this for half-char scrolling) | ||

| + | *reg 4 (##) = y-splitheight-1 (set this inside the current split) | ||

| + | *reg 5 (00) = y-finestart | ||

| + | *reg 6 (25) = y-max visible splitpart (same like 4) | ||

| + | *reg 7 (##) = inside last split -> set to 0; inside first split, but after vblank -> set to 255 | ||

| + | *reg 9 (07) = y-lines/char-1 | ||

| + | |||

| + | Set this inside the previous split: | ||

| + | *reg12 (##) = address high (char / 256 + block * 16) | ||

| + | *reg13 (##) = address low (char mod 256) | ||

| + | |||

| + | Total height of all splits must be 39. | ||

| + | |||

| + | The [https://www.cpcwiki.eu/forum/programming/interrupt-positions-with-various-sized-screens/ IntPos tool] by Kevin Thacker can help visualize the potential split screen areas. | ||

| + | |||

| + | Note: If all you want is multiple graphics modes in the same frame, you don't need to touch the CRTC at all. More information here: [https://www.cpc-power.com/cpcarchives/index.php?page=articles&num=184 Multi-Mode Graphique (FR)] | ||

| + | |||

| + | <br> | ||

| + | |||

| + | == CUDISP (aka CURSOR) == | ||

| + | |||

| + | CUDISP (Cursor Display) signal defines the hardware cursor. | ||

| + | |||

| + | CRTC pin CUDISP is not connected to the Gate Array, so it has no effect on a barebone CPC or Plus machine. | ||

| + | |||

| + | However, this signal is provided to the [[Connector:Expansion port]]. And it is used by the [[PlayCity]] and [[Play2CPC]] expansions. | ||

| + | |||

| + | <br> | ||

| + | |||

| + | == DISPTMG (aka Display Enable) == | ||

| + | |||

| + | DISPTMG (Display Timing) signal defines the border. When DISPTMG is "0" the border colour is output by the Gate Array to the display. | ||

The border has higher priority than pixels but lower priority than the black colour output when HSYNC/VSYNC are active. | The border has higher priority than pixels but lower priority than the black colour output when HSYNC/VSYNC are active. | ||

| + | |||

| + | While border is active, all the CRTC counters continue to increment normally and addresses continue to be generated. | ||

| + | |||

| + | The DISPTMG signal is composited from its 3 internal subcomponents: HBORDER (Horizontal), VBORDER (Vertical), SBORDER (Split) by using the NOR function. DISPTMG is "0" if at least one of its subcomponents is "1". These 3 subcomponents are all independent of each other. | ||

| + | |||

| + | <br> | ||

| + | |||

| + | === HBORDER === | ||

| + | |||

| + | On all CRTCs, HBORDER is disabled when HCC=0 and enabled when HCC=R1. | ||

| + | |||

| + | The exception is for CRTC2 during an HSYNC: the HCC=0 check is skipped, so HBORDER stays on. | ||

| + | |||

| + | <br> | ||

| + | |||

| + | === VBORDER === | ||

| + | |||

| + | On all CRTCs, VBORDER is disabled when VCC=0 and enabled when VCC=R6. | ||

| + | |||

| + | On CRTCs 0/1/2, the condition VCC=R6 is tested on every cycle. | ||

| + | |||

| + | On CRTCs 3/4, the condition VCC=R6 is tested only at each new character line start (when VLC=0 and HCC=0). | ||

| + | |||

| + | <br> | ||

| + | |||

| + | === SBORDER === | ||

| + | |||

| + | Split border is a technique similar to split rasters, except that it is handled by the CRTC instead of the [[Gate Array]]. | ||

| + | |||

| + | DISPTMG can be temporarily forced to 0 by using R8 (DISPTMG Skew) on CRTCs 0/3/4, or by setting R6=0 on CRTC 1. | ||

| + | |||

| + | It is not possible to force DISPTMG on CRTC 2. | ||

| + | |||

| + | <br> | ||

| + | |||

| + | === Border bytes === | ||

| + | |||

| + | Despite their 1MHz clock speed, CRTCs 0/2 have been observed to change state at a rate equivalent to 2MHz chips by responding to both the rising and falling edges of each clock cycle. | ||

| + | |||

| + | ==== Interline border ==== | ||

| + | On CRTCs 0/2, R1>R0 generates one byte (0.5µs) of border at the end of the raster line. On CRTCs 1/3/4, it does not. | ||

| + | |||

| + | To see the border bytes with your own eyes, type this BASIC line after reset: | ||

| + | <pre> | ||

| + | BORDER 6:OUT &BC00,6:OUT &BD00,0 | ||

| + | </pre> | ||

== HSYNC and VSYNC == | == HSYNC and VSYNC == | ||

| Line 152: | Line 367: | ||

|''Register Index''||''Register Name''||''Range''||''CPC Setting''||''Notes'' | |''Register Index''||''Register Name''||''Range''||''CPC Setting''||''Notes'' | ||

|- | |- | ||

| − | |0||Horizontal Total||00000000||63||Width of the screen, in characters. Should always be 63 (64 characters). 1 character == | + | |0||Horizontal Total||00000000||63||Width of the screen, in characters. Should always be 63 (64 characters). 1 character == 1µs. |

|- | |- | ||

|1||Horizontal Displayed||00000000||40||Number of characters displayed. Once horizontal character count (HCC) matches this value, DISPTMG is set to 1. | |1||Horizontal Displayed||00000000||40||Number of characters displayed. Once horizontal character count (HCC) matches this value, DISPTMG is set to 1. | ||

| Line 193: | Line 408: | ||

registers 18-30 read as 0 on type1, register 31 reads as 0x0ff. | registers 18-30 read as 0 on type1, register 31 reads as 0x0ff. | ||

| − | + | <br> | |

| − | + | === Screen size === | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | We can calculate the screen size in words by multiplying R1 x R6 x (R9+1). And then multiplying the result by 2 to have the screen size in bytes. | |

| + | |||

| + | With the default CRTC values, we obtain 40 x 25 x (7+1) x 2 = 16000 bytes. | ||

| + | |||

| + | So we can observe that only part of the 16384 bytes (=16KB) page of VRAM is actually displayed on screen. | ||

| + | |||

| + | <br> | ||

== CRTC Differences == | == CRTC Differences == | ||

| Line 346: | Line 540: | ||

== Horizontal and Vertical Sync (R3) == | == Horizontal and Vertical Sync (R3) == | ||

| − | + | === Horizontal and Vertical Sync (R3) === | |

| − | Bits 7..4 define Vertical Sync Width. If 0 is programmed this gives 16 lines of VSYNC. | + | Type 0: |

| − | Bits 3..0 define Horizontal Sync Width. If 0 is programmed no HSYNC is generated. | + | *Bits 7..4 define Vertical Sync Width. If 0 is programmed, this gives 16 lines of VSYNC. |

| + | *Bits 3..0 define Horizontal Sync Width. If 0 is programmed, no HSYNC is generated (and therefore, no interrupts). | ||

| − | + | Type 1: | |

| + | *Bits 7..4 are ignored. Vertical Sync is fixed at 16 lines. | ||

| + | *Bits 3..0 define Horizontal Sync Width. If 0 is programmed, no HSYNC is generated (and therefore, no interrupts). | ||

| − | Bits 7..4 are ignored. Vertical Sync is fixed at 16 lines. | + | Type 2: |

| − | Bits 3..0 define Horizontal Sync Width. If 0 is programmed | + | *Bits 7..4 are ignored. Vertical Sync is fixed at 16 lines. |

| + | *Bits 3..0 define Horizontal Sync Width. If 0 is programmed, this gives a HSYNC width of 16. | ||

| − | + | Types 3/4: | |

| + | *Bits 7..4 define Vertical Sync Width. If 0 is programmed, this gives 16 lines of VSYNC. | ||

| + | *Bits 3..0 define Horizontal Sync Width. If 0 is programmed, this gives a HSYNC width of 16. | ||

| − | + | <br> | |

| − | + | ||

| − | + | === Interlace and Skew (R8) === | |

| − | Bits 7.. | + | Types 0/3/4: |

| − | Bits 3..0 define | + | *Bits 7..6 define the skew (delay) of the CUDISP signal (00 = Non-skew ; 01 = One-character skew ; 10 = Two-character skew ; 11 = Non-output). |

| + | *Bits 5..4 define the skew (delay) of the DISPTMG signal (00 = Non-skew ; 01 = One-character skew ; 10 = Two-character skew ; 11 = Non-output). | ||

| + | *Bits 3..2 are ignored. | ||

| + | *Bits 1..0 define the interlace mode (00 = No Interlace ; 01 = Interlace Sync ; 10 = No Interlace ; 11 = Interlace Sync and Video). | ||

| − | == | + | Types 1/2: |

| + | *Bits 7..2 are ignored. | ||

| + | *Bits 1..0 define the interlace mode. | ||

| + | |||

| + | <br> | ||

| + | |||

| + | === R31 on Type 1 === | ||

R31 is described in the UM6845R documentation as "Dummy Register". | R31 is described in the UM6845R documentation as "Dummy Register". | ||

| Line 372: | Line 580: | ||

Its use is described in the documentation for the Rockwell R6545 in combination with R18, R19 and R8 and the Status Register. | Its use is described in the documentation for the Rockwell R6545 in combination with R18, R19 and R8 and the Status Register. | ||

| − | In the UM6845R it appears to have no effect. Reading and writing does nothing. Reading it returns | + | In the UM6845R it appears to have no effect. Reading and writing does nothing. Reading it returns &FF. |

| + | |||

| + | R31 doesn't exist on CRTCs 0/2/3/4. | ||

| − | + | <br> | |

== UM6845R and R12/R13 == | == UM6845R and R12/R13 == | ||

| Line 399: | Line 609: | ||

All the other bits read as 0 and don't have any function. | All the other bits read as 0 and don't have any function. | ||

| − | == | + | == CRTC Type Detection == |

| − | + | It is possible to detect the CRTC Type using software methods, and this is done to: | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | * | + | * warn that the software was not designed for the detected 6845 and may function incorrectly |

| + | * to adapt the software so that it will run with the detected 6845 | ||

| + | * In most cases, the type of the detected 6845 is reported | ||

| − | == | + | Detection routine in BASIC: |

| − | + | <pre> | |

| − | + | 10 MODE 1:' Reinitialize screen | |

| + | 20 OUT &BC00,31:IF INP(&BF00)=255 THEN PRINT"crtc 1":END | ||

| + | 30 OUT &BC00,12:IF INP(&BF00)=0 THEN PRINT"crtc 2":END | ||

| + | 40 OUT &BC00,20:IF INP(&BF00)=0 THEN PRINT"crtc 0":END | ||

| + | 50 PRINT"crtc 3/4" | ||

| + | </pre> | ||

| + | Distinguishing between CRTCs 3 and 4 can be done by trying to [[Programming:Unlocking ASIC|unlock the ASIC]] or by testing the [[8255|PPI chip]]. On ASIC, if PPI Port B is set as output it will behave the same as input. | ||

| + | |||

| + | <br> | ||

| + | |||

| + | == CRTC Timing Diagrams == | ||

| + | [[File:CRTC Timing Diagram Rockwell.png]] | ||

| + | |||

| + | <br> | ||

| + | |||

| + | [[File:CRTC timing small.gif]] | ||

| + | |||

| + | <br> | ||

| + | |||

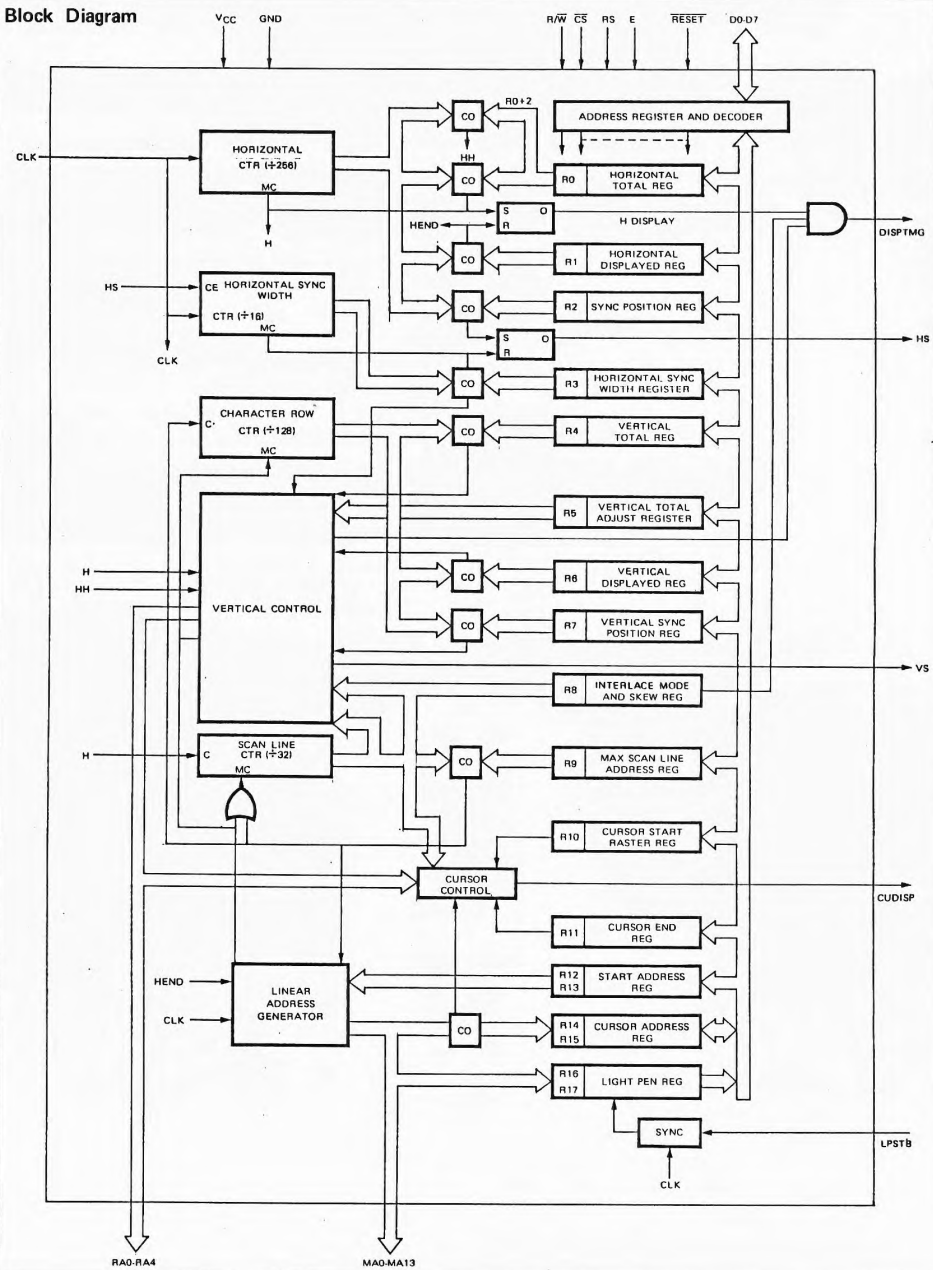

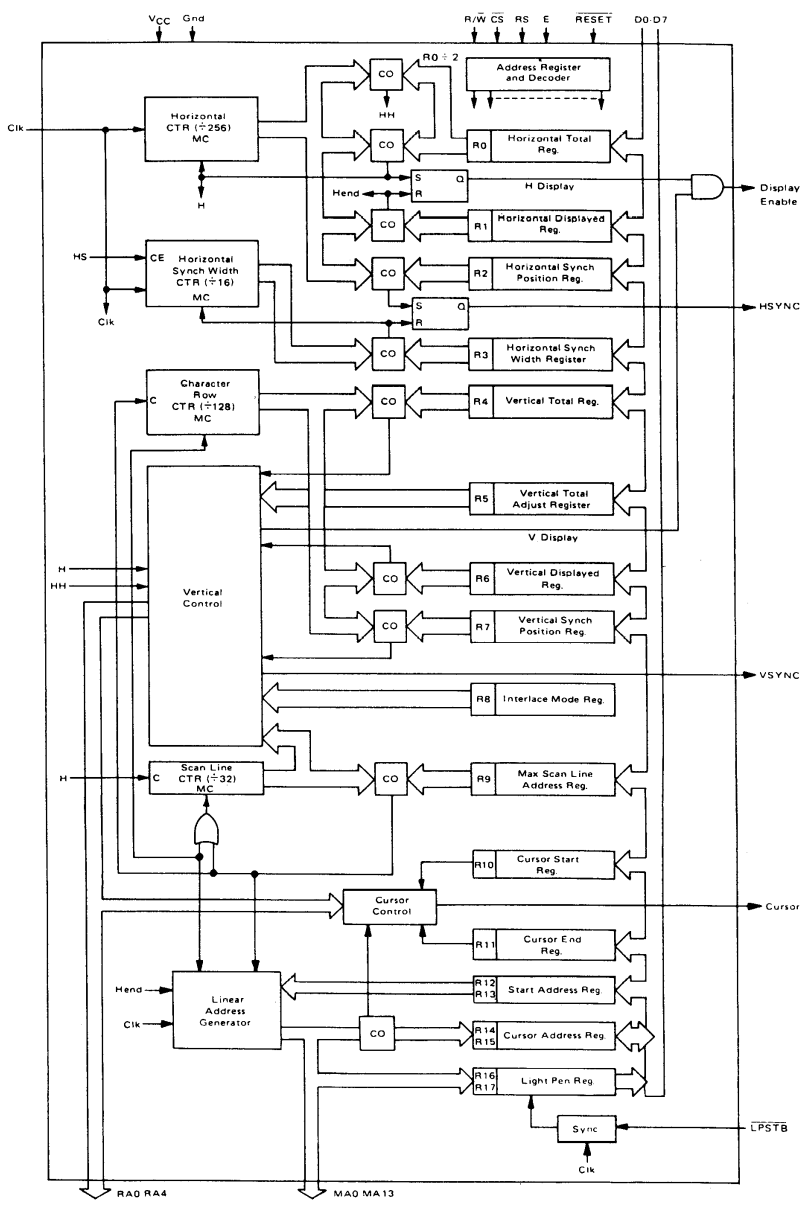

| + | == Block Diagrams == | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | !Hitachi | ||

| + | !UMC | ||

| + | !Motorola | ||

| + | |- | ||

| + | |[[File:CRTC Block Diagram.png|Hitachi]] | ||

| + | |[[File:UMC CRTC Block Diagram.png|UMC]] | ||

| + | |[[File:Motorola CRTC Block Diagram.png|Motorola]] | ||

| + | |} | ||

| + | |||

| + | <br> | ||

| + | |||

| + | == CRTC-II (aka Type 5) == | ||

| + | |||

| + | The [[Media:CRTC-5-HD6345.pdf|HD6345 datasheet]] states it is upward-compatible with the HD6845S in pin and software. | ||

| + | |||

| + | This chip was never used by Amstrad. However, some CPC enthusiasts have replaced the original CRTC chip in their CPC with this one. | ||

| + | |||

| + | With this chip, split-screen becomes easy: [https://thecheshirec.at/2024/05/20/des-splitscreens-en-basic-sur-crtc5/ Split-screen in BASIC]. And 3 new graphics modes (160x100x16c, 320x100x4c, 640x100x2c) are available: [https://thecheshirec.at/2024/11/10/trois-nouveaux-modes-video-grace-au-crtc-5/ New graphics modes in BASIC]. | ||

| + | |||

| + | This is the cheapest way to upgrade the CPC's graphics capabilities, costing only 1.29€. [https://thecheshirec.at/2024/05/19/des-crtc5-a-129e/ Source] | ||

| + | |||

| + | <br> | ||

| + | |||

| + | == Datasheets == | ||

| + | ==== Used by Amstrad ==== | ||

| + | * [[Media:hd6845.hitachi.pdf|HD6845S (Hitachi)]] aka Type 0 | ||

| + | * [[Media:UM6845-UMC.pdf|UM6845 (UMC)]] aka Type 0 | ||

| + | * [[Media:Um6845r.umc.pdf|UM6845R (UMC)]] aka Type 1 | ||

| + | * [[Media:Mc6845.motorola.pdf|MC6845 (Motorola)]] aka Type 2 | ||

| + | * [[Media:CPC_Plus_Asic_Schematic.GIF|AMS40489 (Amstrad)]] aka Type 3 ([[ASIC]]) | ||

| + | * [[AMS40226 (Amstrad)]] aka Type 4 (Pre-ASIC) | ||

| + | |||

| + | <br> | ||

| + | |||

| + | ==== Unused clones ==== | ||

| + | * [[CM607P]] a Bulgarian clone made in Pravetz factory. It is used in the [[Aleste 520EX]]. | ||

| + | * [[Media:hd6845.hitachi.pdf|HD6845R]] by Hitachi. According to Kevin Thacker, the [[KC Compact]] used HD6845R only. | ||

| + | * [[Media:UM6845E-UMC.pdf|UM6845E]] by UMC | ||

| + | * [[Media:Mc6845.pdf|MC6845-1]] by Motorola | ||

| + | * [[Media:F6845.pdf|F6845]] by Fairchild | ||

| + | * [[Media:EF6845P.pdf|EF6845]] by Thomson Semiconductors | ||

| + | * [[Media:VL6845 VTi.pdf|VL6845]] by VTi | ||

| + | * [[Media:C6845 CRTC (CAST).pdf|C6845]] by Cast | ||

| + | * [[Media:MB89321B FUJ.pdf|MB89321B]] by Fujitsu. It is pin-compatible with the 6845 | ||

| + | * [[Media:MB89321A datasheet CRTC.pdf|MB89321A]] by Fujitsu. Enhanced version that adds smooth scroll, screen partitioning, independent scrolling of screen partitions, and other convenient features | ||

| + | * [[Media:Mos 6545-1 crtc.pdf|MOS 6545]] (MOS, Rockwell, Synertek) is pin-compatible with the 6845. Its differences are found in the R8 register. | ||

| + | * [https://www.cpcwiki.eu/forum/other-retro/interesting-discussion-about-the-c128-s-cpm-poor-performance/msg223058/#msg223058 MOS 8563] It is an evolution of the 6545/6845 CRTC chip, with blitter abilities to autonomously perform block memory copies within its dedicated video RAM. | ||

| + | * [https://github.com/hoglet67/BeebFpga/blob/dev/src/common/mc6845.vhd BeebFpga] [https://github.com/MiSTer-devel/Amstrad_MiSTer/blob/master/rtl/UM6845R.v MiSTer] [https://opencores.org/websvn/filedetails?repname=System09&path=%2FSystem09%2Ftrunk%2Frtl%2FVHDL%2Fcrtc6845.vhd OpenCores] Verilog/VHDL implementations of the 6845 | ||

| + | |||

| + | <br> | ||

== Tools about CRTC == | == Tools about CRTC == | ||

| − | * | + | * [http://www.cpcwiki.eu/imgs/9/99/Elmar_Krieger-SPECIAL_EFFECTS.dsk some BASIC tools to detect CRTC types 0-1-2 and show some effects] by [[Elmar Krieger]] (DSK for Emulators) |

| + | * [[File:Shaker26.dsk]] Shaker - Suite of CRTC tests associated with the CPC CRTC compendium (many of them will not work correctly on emulators and that was the purpose of the tests, to help create more compatible emulation) | ||

| + | * [[File:Shaker addon.dsk]] Shaker Add-On (Pixel 1 Hard Scroll / Vertical Rupture all Crtc) | ||

| + | |||

| + | <br> | ||

== Links == | == Links == | ||

* [http://en.wikipedia.org/wiki/6845 Wikipedia on the CRTC] | * [http://en.wikipedia.org/wiki/6845 Wikipedia on the CRTC] | ||

| − | * [http://www.grimware.org/doku.php/documentations/devices/crtc | + | * [[Media:ACCC1.8-EN.pdf]] CPC CRTC Compendium - Latest (04/2024!) document containing in-depth info about CRTC programming on CPC. |

| − | * [http:// | + | * [[Media:CRTC Compendium Podcast.mp3]] The CRTC Compendium digested in podcast format |

| + | * [http://www.grimware.org/doku.php/documentations/devices/crtc CRTC documentation from Grimware] | ||

| + | * [http://quasar.cpcscene.net/doku.php?id=assem:crtc Quasar CRTC documentation (in french)] | ||

| + | * [https://pulkomandy.github.io/shinra.github.io/crtc.html PulkoMandy's table] [https://www.theoddys.com/acorn/the_6845_crtc/6845%20Variants.xlsx Oddy's table] Differences between CRTC types | ||

| + | * [[Media:Dossier Rupture(Gozeur Paradox).pdf]] | ||

| + | * [[Media:Dossier CRTC(Ramlaid Mortel).pdf]] Les entrailles du CRTC | ||

| + | * [https://thecheshirec.at/tag/crtc6845/ Leçons CRTC (CheshireCat)] | ||

| + | * [https://martin.hinner.info/vga/pal.html PAL video timing specification] | ||

==Related pages== | ==Related pages== | ||

| Line 433: | Line 725: | ||

*[[Synchronising with the CRTC and display]] : technic and details on the relationship between Gate Array and CRTC. | *[[Synchronising with the CRTC and display]] : technic and details on the relationship between Gate Array and CRTC. | ||

| − | [[Category:Hardware]] [[Category:CPC Internal Components]] [[Category:Programming]] [[Category:Datasheet]] [[Category:Graphic]] | + | *[[VIDI digitizer]] This extension contains its own CRTC chip |

| + | |||

| + | [[Category:Hardware]] [[Category:CPC Internal Components]] [[Category:Electronic Component]] [[Category:Programming]] [[Category:Datasheet]] [[Category:Graphic]] | ||

Latest revision as of 13:47, 29 May 2025

The 6845 CRTC (Cathode Ray Tube Controller) chip was created by Motorola in 1977. It works with the Gate Array to generate the video signal on the Amstrad CPC.

This chip is also used in the BBC Micro, Camputers Lynx, EG2000 Colour Genie, Sharp X1, MicroBee, Commodore PET and the early graphics cards (MDA, Hercules, CGA, Plantronics Colorplus) for IBM PC. And it is found in some MSX1 expansions, providing an 80-column text mode.

It's important to note that the CRTC chip is primarily designed for character-based displays. It explains why, on the Amstrad CPC, the video memory is organized into a grid of characters rather than a purely linear bitmap.

NOTE: This document describes the functionality in terms of the CPC with its separate CRTC and Gate-Array. The Plus has both integrated into the same IC, but could be considered to have two functional blocks, one for CRTC and one for Gate-Array. In this document the term 'Gate-Array' is used, but this also applies to the ASIC.

Contents

- 1 Overview

- 2 Timings and relating with Z80 instructions count

- 3 Programming

- 4 Addressing

- 5 Split screen (aka Rupture)

- 6 CUDISP (aka CURSOR)

- 7 DISPTMG (aka Display Enable)

- 8 HSYNC and VSYNC

- 9 The 6845 Registers

- 10 CRTC Differences

- 11 Horizontal and Vertical Sync (R3)

- 12 UM6845R and R12/R13

- 13 UM6845R status register

- 14 CRTC Type Detection

- 15 CRTC Timing Diagrams

- 16 Block Diagrams

- 17 CRTC-II (aka Type 5)

- 18 Datasheets

- 19 Tools about CRTC

- 20 Links

- 21 Related pages

Overview

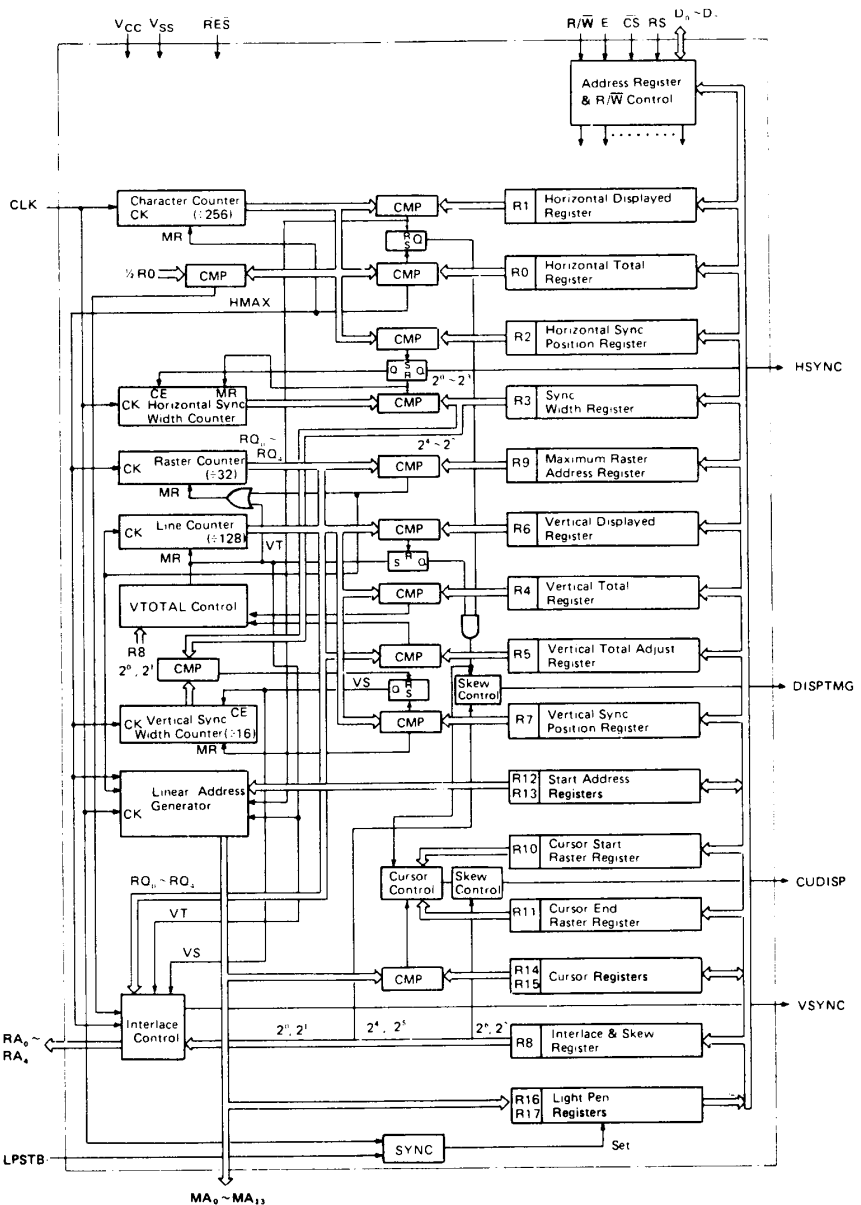

The 6845 Cathode Ray Tube Controller (CRTC) is a programmable IC used to generate video displays. This IC is used in a variety of computers including the Amstrad CPC, Amstrad CPC+ and KC Compact.

The CRTC is a simple chip. It is made up of counters and equality operators, tied by simple logic. All the complexity stems from its multiple independent implementations with their subtle differences.

The CRTC was a common part available from many different manufacturers. During the life of the CPC, Amstrad sourced the CRTC from various manufacturers.

All ICs used were based on the same design but have a different implementation. As a result they do not operate identically in all situations. This document highlights these differences.

This table lists the known ICs used, with their part number, manufacturer and type number.

| Part number | Manufacturer | Type number (note 3) |

| HD6845S | Hitachi | 0 |

| UM6845 | UMC | 0 |

| UM6845R | UMC | 1 |

| MC6845 | Motorola | 2 |

| AMS40489 | Amstrad | 3 (note 1) |

| 40226 | Amstrad | 4 (note 2) |

NOTES

1. The CRTC functionality is integrated into the CPC+ ASIC. This type exists only in the CPC464+,CPC6128+ and GX4000.

2. This type exists in "cost-down" CPC464 and CPC6128 systems. In the "cost-down" the CRTC functionality is integrated into a single ASIC IC. This ASIC is often refered to as the "Pre-ASIC" because it preceeded the CPC+ ASIC. The CRTC functionality of the Pre-ASIC is almost identical to the CRTC within the ASIC.

3. In the Amstrad community each 6845 implementation has been assigned a type number. This type identifies a group of implementations which operate in exactly the same way.

As far as I know, the type number system was originally used by demo programmers.

It is possible to detect the 6845 present using software methods, and this is done to:

- warn that the software was not designed for the detected 6845 and may function incorrectly,

- to adapt the software so that it will run with the detected 6845

- In most cases, the type of the detected 6845 is reported.

4. As far as I know, the KC compact used HD6845R only.

Timings and relating with Z80 instructions count

Some informations like : how many Z80 instructions can I fit within a scan line ? Within a screen ? Etc... See http://www.cpcwiki.eu/forum/programming/frame-flyback-and-interrupts/msg25106/#msg25106 (To be extracted/edited to conform to wiki good practices).

Programming

The 6845 is selected when bit 14 of the I/O port address is set to "0". Bit 9 and 8 of the I/O port address define the function to access. The remaining bits can be any value, but it is adviseable to set these to "1" to avoid conflict with other devices in the system.

The recommended I/O port addresses are:

| I/O port address | /CS (A14) | R/W (A9) | RS (A8) | Function | Read/Write |

|---|---|---|---|---|---|

| &BCxx | 0 | 0 | 0 | Select 6845 register | Write only |

| &BDxx | 0 | 0 | 1 | Write to selected internal 6845 register | Write only |

| &BExx | 0 | 1 | 0 |

|

Read only |

| &BFxx | 0 | 1 | 1 | Read from selected internal 6845 register | Read only |

The CRTC is not connected to the CPU's RD and WR pins, so it cannot detect the bus's I/O direction. Therefore, executing an IN instruction to the select or write functions causes the CRTC to write the unpredictable data provided by the high-impedance bus to its registers.

Addressing

The VMA of the Gate Array is constructed from the CRTC MA and RA signals:

| Video Memory Address | Signal source | Signal name |

|---|---|---|

| A15 | 6845 | MA13 |

| A14 | 6845 | MA12 |

| A13 | 6845 | RA2 |

| A12 | 6845 | RA1 |

| A11 | 6845 | RA0 |

| A10 | 6845 | MA9 |

| A9 | 6845 | MA8 |

| A8 | 6845 | MA7 |

| A7 | 6845 | MA6 |

| A6 | 6845 | MA5 |

| A5 | 6845 | MA4 |

| A4 | 6845 | MA3 |

| A3 | 6845 | MA2 |

| A2 | 6845 | MA1 |

| A1 | 6845 | MA0 |

| A0 | Gate-Array | CCLK |

CRTC generates the address, Gate Array reads the data and converts it to pixels based on its current graphics mode and palette.

CRTC pins RA3, RA4, MA10, MA11 are not connected on CPC.

Overscan bits

It is possible to use 32KB screen size (used for overscan) by setting bits 11 and 10 of Register 12 both to 1. Bits MA11 and MA10 of the address generated by the CRTC are not written on the address bus to access video memory; settings both bits to 1 is the only way to cause a carry to bit MA12 when address pass over the end of current video page to change the memory address to the next video page.

| Register 12 | Register 13 | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Unused | Video Page | Page Size | Start Address (1024 positions) | ||||||||||||

|

|

Coarse hardware scrolling

The start address can be manipulated to achieve horizontal and/or vertical hardware scrolling:

- To move right:

start_address := start_address + 1 - To move left:

start_address := start_address - 1 - To move down:

start_address := start_address + R1 - To move up:

start_address := start_address - R1

However, it is a position in word (16 bits), not in byte. So, the screen will move two bytes at a time horizontally. Also, the precision will be one CRTC character vertically.

The first game that used R12/R13 for both horizontal and vertical hardware scrolling is Roland on the Ropes, released in 1984.

The following BASIC program demonstrates the coarse scrolling by setting the R12 and R13 registers based on keyboard input:

10 ma%=0 20 IF INKEY(1)=0 THEN GOSUB 100 30 IF INKEY(2)=0 THEN GOSUB 300 40 IF INKEY(8)=0 THEN GOSUB 500 50 IF INKEY(0)=0 THEN GOSUB 700 60 GOTO 20 100 ' right 110 ma%=ma%+1: GOSUB 900: RETURN 300 ' down 310 ma%=ma%+40: GOSUB 900: RETURN 500 ' left 510 ma%=ABS(ma%-1): GOSUB 900: RETURN 700 ' up 710 ma%=ABS(ma%-40): GOSUB 900: RETURN 900 ' set R12 and R13 910 l%=ma% AND 255: h%=&30 OR ((ma%\256) AND 3) :OUT &BC00,13:OUT &BD00,l%: OUT &BC00,12:OUT &BD00,h% 930 RETURN

Which looks like the following:

Advanced hardware scrolling

To achieve smoother hardware scrolling, other tricks are required in complement to R12/R13. Usually, R3 is used for smooth horizontal scroll and R5 for smooth vertical scroll.

A good example of smooth hardware multidirectional scrolling game on CPC is Super Cauldron, released in 1993.

Everything you need to know about hardware scrolling on CPC can be found there.

Split screen (aka Rupture)

While there is usually 1 CRTC frame per screen frame, the screen frame can be divided into multiple CRTC frames of varying proportions.

This is useful for defining different scrolling zones in your screen frame. For example, it was used for hardware parallax scrolling in the game The Living Daylights, released in 1987. Source

And this is basically the bread and butter of innumerable CPC demos.

Some rules of thumb Source:

- changes to the screen address have to be done anywhere in the previous split

- changes to the height of the split have to be done inside the current split (after it has started, in the area of the size of the previous split)

- changes to screen mode and colours are happening immediately

CRTC registers and screen splitting:

- reg 0 (63) = x-screenwidth (usually always 63)

- reg 1 (50) = x-splitwidth (e.g.50)

- reg 2 (51) = x-splitstart (e.g. 51)

- reg 3 (08) = x-finestart (maybe use this for half-char scrolling)

- reg 4 (##) = y-splitheight-1 (set this inside the current split)

- reg 5 (00) = y-finestart

- reg 6 (25) = y-max visible splitpart (same like 4)

- reg 7 (##) = inside last split -> set to 0; inside first split, but after vblank -> set to 255

- reg 9 (07) = y-lines/char-1

Set this inside the previous split:

- reg12 (##) = address high (char / 256 + block * 16)

- reg13 (##) = address low (char mod 256)

Total height of all splits must be 39.

The IntPos tool by Kevin Thacker can help visualize the potential split screen areas.

Note: If all you want is multiple graphics modes in the same frame, you don't need to touch the CRTC at all. More information here: Multi-Mode Graphique (FR)

CUDISP (aka CURSOR)

CUDISP (Cursor Display) signal defines the hardware cursor.

CRTC pin CUDISP is not connected to the Gate Array, so it has no effect on a barebone CPC or Plus machine.

However, this signal is provided to the Connector:Expansion port. And it is used by the PlayCity and Play2CPC expansions.

DISPTMG (aka Display Enable)

DISPTMG (Display Timing) signal defines the border. When DISPTMG is "0" the border colour is output by the Gate Array to the display.

The border has higher priority than pixels but lower priority than the black colour output when HSYNC/VSYNC are active.

While border is active, all the CRTC counters continue to increment normally and addresses continue to be generated.

The DISPTMG signal is composited from its 3 internal subcomponents: HBORDER (Horizontal), VBORDER (Vertical), SBORDER (Split) by using the NOR function. DISPTMG is "0" if at least one of its subcomponents is "1". These 3 subcomponents are all independent of each other.

HBORDER

On all CRTCs, HBORDER is disabled when HCC=0 and enabled when HCC=R1.

The exception is for CRTC2 during an HSYNC: the HCC=0 check is skipped, so HBORDER stays on.

VBORDER

On all CRTCs, VBORDER is disabled when VCC=0 and enabled when VCC=R6.

On CRTCs 0/1/2, the condition VCC=R6 is tested on every cycle.

On CRTCs 3/4, the condition VCC=R6 is tested only at each new character line start (when VLC=0 and HCC=0).

SBORDER

Split border is a technique similar to split rasters, except that it is handled by the CRTC instead of the Gate Array.

DISPTMG can be temporarily forced to 0 by using R8 (DISPTMG Skew) on CRTCs 0/3/4, or by setting R6=0 on CRTC 1.

It is not possible to force DISPTMG on CRTC 2.

Border bytes

Despite their 1MHz clock speed, CRTCs 0/2 have been observed to change state at a rate equivalent to 2MHz chips by responding to both the rising and falling edges of each clock cycle.

Interline border

On CRTCs 0/2, R1>R0 generates one byte (0.5µs) of border at the end of the raster line. On CRTCs 1/3/4, it does not.

To see the border bytes with your own eyes, type this BASIC line after reset:

BORDER 6:OUT &BC00,6:OUT &BD00,0

HSYNC and VSYNC

On CPC, HSYNC and VSYNC from the CRTC are passed into the Gate-Array.

When HSYNC is active Gate-Array outputs the palette colour black. If the HSYNC is set to 14 characters then black will be output for 14us.

The HSYNC is modified before being sent to the monitor. It happens 2us after the HSYNC from the CRTC and lasts 4us when HSYNC length is greater or equal to 6.

If R2=46, and HSYNC width is 14 then monitor hsync starts at 48 and lasts until 51.

On a CPC monitor, the HSYNC is rendered in "absolute black". It is darker than the black output by the Gate-Array.

The VSYNC is also modified before being sent to the monitor. It happens two lines* after the VSYNC from the CRTC and stay two lines (same cut rule if VSYNC is lower than 4). PAL (50Hz) does need two lines VSYNC_width, and 4us HSYNC_width.

Using CRTC1, VSYNC width value 0 means a value of 16.

The 6845 Registers

The Internal registers of the 6845 are:

| Register Index | Register Name | Range | CPC Setting | Notes |

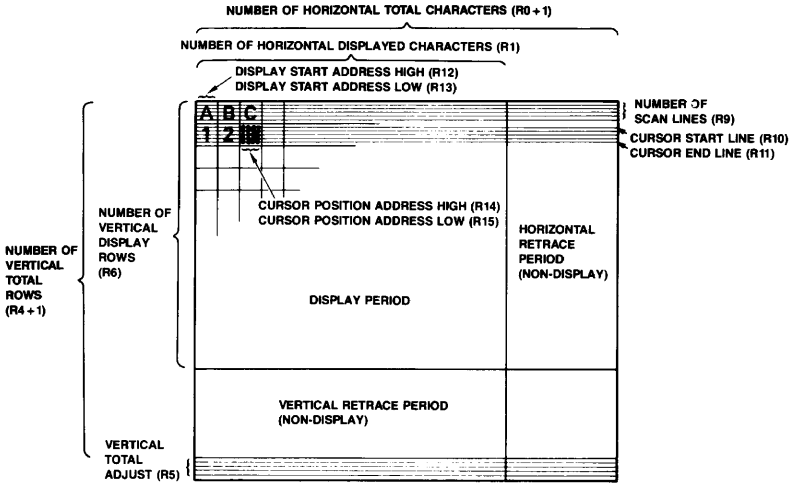

| 0 | Horizontal Total | 00000000 | 63 | Width of the screen, in characters. Should always be 63 (64 characters). 1 character == 1µs. |

| 1 | Horizontal Displayed | 00000000 | 40 | Number of characters displayed. Once horizontal character count (HCC) matches this value, DISPTMG is set to 1. |

| 2 | Horizontal Sync Position | 00000000 | 46 | When to start the HSync signal. |

| 3 | Horizontal and Vertical Sync Widths | VVVVHHHH | 128+14 | HSync pulse width in characters (0 means 16 on some CRTC), should always be more than 8; VSync width in scan-lines. (0 means 16 on some CRTC. Not present on all CRTCs, fixed to 16 lines on these) |

| 4 | Vertical Total | x0000000 | 38 | Height of the screen, in characters. |

| 5 | Vertical Total Adjust | xxx00000 | 0 | Measured in scanlines, can be used for smooth vertical scrolling on CPC. |

| 6 | Vertical Displayed | x0000000 | 25 | Height of displayed screen in characters. Once vertical character count (VCC) matches this value, DISPTMG is set to 1. |

| 7 | Vertical Sync position | x0000000 | 30 | When to start the VSync signal, in characters. |

| 8 | Interlace and Skew | xxxxxx00 | 0 | 00: No interlace; 01: Interlace Sync Raster Scan Mode; 10: No Interlace; 11: Interlace Sync and Video Raster Scan Mode |

| 9 | Maximum Raster Address | xxx00000 | 7 | Maximum scan line address on CPC can hold between 0 and 7, higher values' upper bits are ignored |

| 10 | Cursor Start Raster | xBP00000 | 0 | Cursor not used on CPC. B = Blink On/Off; P = Blink Period Control (Slow/Fast). Sets first raster row of character that cursor is on to invert. |

| 11 | Cursor End Raster | xxx00000 | 0 | Sets last raster row of character that cursor is on to invert |

| 12 | Display Start Address (High) | xx000000 | 48 | |

| 13 | Display Start Address (Low) | 00000000 | 0 | Allows you to offset the start of screen memory for hardware scrolling, and if using memory from address &0000 with the firmware. |

| 14 | Cursor Address (High) | xx000000 | 0 | |

| 15 | Cursor Address (Low) | 00000000 | 0 | |

| 16 | Light Pen Address (High) | xx000000 | Read Only | |

| 17 | Light Pen Address (Low) | 00000000 | Read Only |

registers 18-31 read as 0, on type 0 and 2. registers 18-30 read as 0 on type1, register 31 reads as 0x0ff.

Screen size

We can calculate the screen size in words by multiplying R1 x R6 x (R9+1). And then multiplying the result by 2 to have the screen size in bytes.

With the default CRTC values, we obtain 40 x 25 x (7+1) x 2 = 16000 bytes.

So we can observe that only part of the 16384 bytes (=16KB) page of VRAM is actually displayed on screen.

CRTC Differences

In this section I will attempt to identify all the differences between each CRTC.

The following tables list the functions that can be accessed for each type:

Type 0

| b1 | b0 | Function | Read/Write |

| 0 | 0 | Select internal 6845 register | Write Only |

| 0 | 1 | Write to selected internal 6845 register | Write Only |

| 1 | 0 | - | - |

| 1 | 1 | Read from selected internal 6845 register | Read only |

Type 1

| b1 | b0 | Function | Read/Write |

| 0 | 0 | Select internal 6845 register | Write Only |

| 0 | 1 | Write to selected internal 6845 register | Write Only |

| 1 | 0 | Read Status Register | Read Only |

| 1 | 1 | Read from selected internal 6845 register | Read only |

Type 2

| b1 | b0 | Function | Read/Write |

| 0 | 0 | Select internal 6845 register | Write Only |

| 0 | 1 | Write to selected internal 6845 register | Write Only |

| 1 | 0 | - | - |

| 1 | 1 | Read from selected internal 6845 register | Read only |

Type 3 and 4

| b1 | b0 | Function | Read/Write |

| 0 | 0 | Select internal 6845 register | Write Only |

| 0 | 1 | Write to selected internal 6845 register | Write Only |

| 1 | 0 | Read from selected internal 6845 register | Read Only |

| 1 | 1 | Read from selected internal 6845 register | Read only |

It is not possible to read from all the internal registers, this table shows the read/write status of each register for each type:

| Register Index | Register Name | Type | ||||

| 0 | 1 | 2 | 3 | 4 | ||

| 0 | Horizontal Total | Write Only | Write Only | Write Only | (note 2) | (note 3) |

| 1 | Horizontal Displayed | Write Only | Write Only | Write Only | (note 2) | (note 3) |

| 2 | Horizontal Sync Position | Write Only | Write Only | Write Only | (note 2) | (note 3) |

| 3 | Horizontal and Vertical Sync Widths | Write Only | Write Only | Write Only | (note 2) | (note 3) |

| 4 | Vertical Total | Write Only | Write Only | Write Only | (note 2) | (note 3) |

| 5 | Vertical Total Adjust | Write Only | Write Only | Write Only | (note 2) | (note 3) |

| 6 | Vertical Displayed | Write Only | Write Only | Write Only | (note 2) | (note 3) |

| 7 | Vertical Sync position | Write Only | Write Only | Write Only | (note 2) | (note 3) |

| 8 | Interlace and Skew | Write Only | Write Only | Write Only | (note 2) | (note 3) |

| 9 | Maximum Raster Address | Write Only | Write Only | Write Only | (note 2) | (note 3) |

| 10 | Cursor Start Raster | Write Only | Write Only | Write Only | (note 2) | (note 3) |

| 11 | Cursor End Raster | Write Only | Write Only | Write Only | (note 2) | (note 3) |

| 12 | Display Start Address (High) | Read/Write | Write Only | Write Only | Read/Write (note 2) | (note 3) |

| 13 | Display Start Address (Low) | Read/Write | Write Only | Write Only | Read/Write (note 2) | (note 3) |

| 14 | Cursor Address (High) | Read/Write | Read/Write | Read/Write | Read/Write (note 2) | (note 3) |

| 15 | Cursor Address (Low) | Read/Write | Read/Write | Read/Write | Read/Write (note 2) | (note 3) |

| 16 | Light Pen Address (High) | Read Only | Read Only | Read Only | Read Only (note 2) | (note 3) |

| 17 | Light Pen Address (Low) | Read Only | Read Only | Read Only | Read Only (note 2) | (note 3) |

Notes

1. On type 0 and 1, if a Write Only register is read from, "0" is returned.

2. See the document "Extra CPC Plus Hardware Information" for more details.

3. CRTC type 4 is the same as CRTC type 3. The registers also repeat as they do on the type 3.

Horizontal and Vertical Sync (R3)

Horizontal and Vertical Sync (R3)

Type 0:

- Bits 7..4 define Vertical Sync Width. If 0 is programmed, this gives 16 lines of VSYNC.

- Bits 3..0 define Horizontal Sync Width. If 0 is programmed, no HSYNC is generated (and therefore, no interrupts).

Type 1:

- Bits 7..4 are ignored. Vertical Sync is fixed at 16 lines.

- Bits 3..0 define Horizontal Sync Width. If 0 is programmed, no HSYNC is generated (and therefore, no interrupts).

Type 2:

- Bits 7..4 are ignored. Vertical Sync is fixed at 16 lines.

- Bits 3..0 define Horizontal Sync Width. If 0 is programmed, this gives a HSYNC width of 16.

Types 3/4:

- Bits 7..4 define Vertical Sync Width. If 0 is programmed, this gives 16 lines of VSYNC.

- Bits 3..0 define Horizontal Sync Width. If 0 is programmed, this gives a HSYNC width of 16.

Interlace and Skew (R8)

Types 0/3/4:

- Bits 7..6 define the skew (delay) of the CUDISP signal (00 = Non-skew ; 01 = One-character skew ; 10 = Two-character skew ; 11 = Non-output).

- Bits 5..4 define the skew (delay) of the DISPTMG signal (00 = Non-skew ; 01 = One-character skew ; 10 = Two-character skew ; 11 = Non-output).

- Bits 3..2 are ignored.

- Bits 1..0 define the interlace mode (00 = No Interlace ; 01 = Interlace Sync ; 10 = No Interlace ; 11 = Interlace Sync and Video).

Types 1/2:

- Bits 7..2 are ignored.

- Bits 1..0 define the interlace mode.

R31 on Type 1

R31 is described in the UM6845R documentation as "Dummy Register".

Its use is described in the documentation for the Rockwell R6545 in combination with R18, R19 and R8 and the Status Register.

In the UM6845R it appears to have no effect. Reading and writing does nothing. Reading it returns &FF.

R31 doesn't exist on CRTCs 0/2/3/4.

UM6845R and R12/R13

The UM6845R differs to other CRTC in respect of R12/R13.

When VCC=0, R12/R13 is re-read at the start of each line. R12/R13 can therefore be changed for each scanline when VCC=0.

Just like other CRTCs when RC==(R9-1), the current MA is captured for the next char-line.

In demos to make a display compatible with all CRTCs program R12/R13 when VCC!=0. This will then take effect at the next frame start.

UM6845R status register

The UM6845R has a status register that can be read using port &BExx.

Bit 6 is set to 1 if there is a strobe input to the /LPEN signal. It is cleared to 0 when either R17 or R16 (LPEN address) of the CRTC are read. It signals there is a valid LPEN input. On my CPC (arnoldemu) with UM6845R, it is triggered at power on, R17 and R16 have the values 0 when read.

Bit 5 is set to 1 when CRTC is in "vertical blanking". Vertical blanking is when the vertical border is active. i.e. VCC>=R6.

It is cleared when the frame is started (VCC=0). It is not directly related to the DISPTMG output (used by the CPC to display the border colour) because that output is a combination of horizontal and vertical blanking. This bit will be 0 when pixels are being displayed.

All the other bits read as 0 and don't have any function.

CRTC Type Detection

It is possible to detect the CRTC Type using software methods, and this is done to:

- warn that the software was not designed for the detected 6845 and may function incorrectly

- to adapt the software so that it will run with the detected 6845

- In most cases, the type of the detected 6845 is reported

Detection routine in BASIC:

10 MODE 1:' Reinitialize screen 20 OUT &BC00,31:IF INP(&BF00)=255 THEN PRINT"crtc 1":END 30 OUT &BC00,12:IF INP(&BF00)=0 THEN PRINT"crtc 2":END 40 OUT &BC00,20:IF INP(&BF00)=0 THEN PRINT"crtc 0":END 50 PRINT"crtc 3/4"

Distinguishing between CRTCs 3 and 4 can be done by trying to unlock the ASIC or by testing the PPI chip. On ASIC, if PPI Port B is set as output it will behave the same as input.

CRTC Timing Diagrams

Block Diagrams

| Hitachi | UMC | Motorola |

|---|---|---|

|

|

|

CRTC-II (aka Type 5)

The HD6345 datasheet states it is upward-compatible with the HD6845S in pin and software.

This chip was never used by Amstrad. However, some CPC enthusiasts have replaced the original CRTC chip in their CPC with this one.

With this chip, split-screen becomes easy: Split-screen in BASIC. And 3 new graphics modes (160x100x16c, 320x100x4c, 640x100x2c) are available: New graphics modes in BASIC.

This is the cheapest way to upgrade the CPC's graphics capabilities, costing only 1.29€. Source

Datasheets

Used by Amstrad

- HD6845S (Hitachi) aka Type 0

- UM6845 (UMC) aka Type 0

- UM6845R (UMC) aka Type 1

- MC6845 (Motorola) aka Type 2

- AMS40489 (Amstrad) aka Type 3 (ASIC)

- AMS40226 (Amstrad) aka Type 4 (Pre-ASIC)

Unused clones

- CM607P a Bulgarian clone made in Pravetz factory. It is used in the Aleste 520EX.

- HD6845R by Hitachi. According to Kevin Thacker, the KC Compact used HD6845R only.

- UM6845E by UMC

- MC6845-1 by Motorola

- F6845 by Fairchild

- EF6845 by Thomson Semiconductors

- VL6845 by VTi

- C6845 by Cast

- MB89321B by Fujitsu. It is pin-compatible with the 6845

- MB89321A by Fujitsu. Enhanced version that adds smooth scroll, screen partitioning, independent scrolling of screen partitions, and other convenient features

- MOS 6545 (MOS, Rockwell, Synertek) is pin-compatible with the 6845. Its differences are found in the R8 register.

- MOS 8563 It is an evolution of the 6545/6845 CRTC chip, with blitter abilities to autonomously perform block memory copies within its dedicated video RAM.

- BeebFpga MiSTer OpenCores Verilog/VHDL implementations of the 6845

Tools about CRTC

- some BASIC tools to detect CRTC types 0-1-2 and show some effects by Elmar Krieger (DSK for Emulators)

- File:Shaker26.dsk Shaker - Suite of CRTC tests associated with the CPC CRTC compendium (many of them will not work correctly on emulators and that was the purpose of the tests, to help create more compatible emulation)

- File:Shaker addon.dsk Shaker Add-On (Pixel 1 Hard Scroll / Vertical Rupture all Crtc)

Links

- Wikipedia on the CRTC

- Media:ACCC1.8-EN.pdf CPC CRTC Compendium - Latest (04/2024!) document containing in-depth info about CRTC programming on CPC.

- Media:CRTC Compendium Podcast.mp3 The CRTC Compendium digested in podcast format

- CRTC documentation from Grimware

- Quasar CRTC documentation (in french)

- PulkoMandy's table Oddy's table Differences between CRTC types

- Media:Dossier Rupture(Gozeur Paradox).pdf

- Media:Dossier CRTC(Ramlaid Mortel).pdf Les entrailles du CRTC

- Leçons CRTC (CheshireCat)

- PAL video timing specification

Related pages

- Synchronising with the CRTC and display : technic and details on the relationship between Gate Array and CRTC.

- VIDI digitizer This extension contains its own CRTC chip