# **Advanced Products**

# **FUJITSU**

## MB89321A, MB89322A **CMOS Programmable CRT Controller**

October 1986 Edition 1.0

#### Description

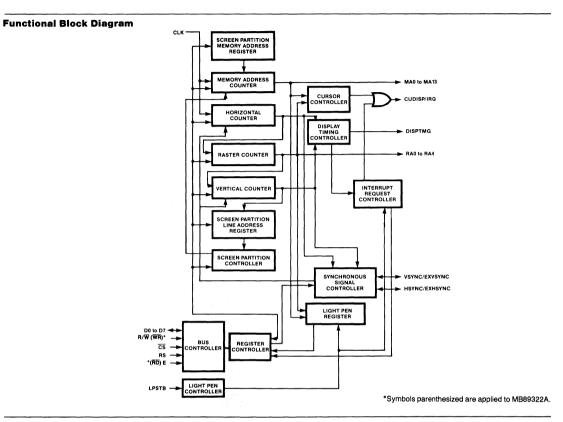

The MB89321A/MB89322A Programmable CRT Controllers are single chip CMOS devices used to interface CRT raster scan displays with microcomputer systems. Both devices operate on a single +5 V power supply and have TTL-compatible I/O. The MB89321A interfaces to 6800 family microprocessors; the MB89322A to the 8080.

The MB89321A/MB89322A refresh the display by buffering information from main memory using thirty-three internal registers and keeping track of the display position of the screen. Both devices are designed to allow simple interfacing to most raster scan CRTs with a minimum of external hardware and software overhead.

#### **Features**

- Programmable Screen and **Character Formats**

- **Cursor Control (3 types)**

- Selectable Scan Modes (3) types)

- Light Pen Detection

- Refresh Memory Address Function

- Screen Partitioning (up to 4 partitions)

- Independent Paging/Scrolling for Each

- Screen Partition Smooth Scrolling (up to 4 screens simultaneously)

- Status Generation and Processor Interrupt Generation by Vertical Blanking or Light Pen

- External Sync for TV Superimposition (synchronous mode) or Interface to Other CRT **Controllers (master-slave** mode)

- Double-Size Vertical Display using Raster Interpolation

- 4.0 MHz Clock Rate

- Single +5 V Power Supply

CMOS Process

- 40-pin Plastic DIP

#### **Pin Assignment**

\*Symbols parenthesized are applied to MB89322A.

4

#### Pin Descriptions MB89321A(MB89322A)

Pin Pin Number Symbol Name Function Ground Ground Vss Input used for device reset. When RESET goes low: Internal counters are cleared and stopped; All outputs go low, and; Control registers and status register are cleared, other RESET 2 Reset internal registers unaffected. Enabled only when LPSTB is low. RESET goes high, display is initiated immediately. Control registers R30 and R31 must be initialized by software after reset is released. Character detection input. When high, the memory address Light Pen LPSTB is loaded in the light pen register, the raster address in the 3 Strobe light pen raster register, and the status bit set. 4 to MA0 to Memory Refresh memory address output 17 **MA13** Address Display 18 DISPTMG Display timing output. Set to high during display. Timing Cursor Cursor display timing output/interrupt request output. Set Display CUDISP/ to high during display. Setting the control register enables 19 Timing/ IRO a high-level interrupt request signal to be output while the Interrupt display timing signal is low. Request Power 20 Vcc +5 V power supply. Supply CLK 21 Clock Clock input. Goes low during EXHSYNC in TV sync mode. R/W Read/Write MPU read/write input. 22 (MPU write input) (WR)\* (Write) MPU enable input. Enable F 23 (RD)\* (MPU read input) (Read) Internal register select input. Normally connected to the Register 24 RS least significant bit (A0) of the address bus. When high, select selects internal registers; when low, the address register. Chip Chip select input. Goes low when the MPU accesses the CS 25 select CRTC. 26 to D7 to Data Bus MPU data bus pins 33 D0 34 to RA4 to Raster Raster address output 38 RA0 Address Hsync HSYNC/ Output/ Horizontal sync output/external horizontal sync input. 39 EXHSYNC Hsync When reset, becomes the horizontal sync output. Input Vsvnc VSYNC/ Output/ Vertical sync output/external vertical sync input. When 40 EXVSYNC Vsync reset, becomes the vertical sync output. Input

\*Symbols parenthesized are applied to MB89322A.

#### Internal Registers and Functions

|    |                    | Address |                    |               |               |   | Deniete- |                                           |             |         | Data Bit |       |       |        |       |

|----|--------------------|---------|--------------------|---------------|---------------|---|----------|-------------------------------------------|-------------|---------|----------|-------|-------|--------|-------|

| CS | RS 4 3 2 1 0 Numbe |         | Register<br>Number | Register Name | Read<br>Write |   |          |                                           | 4 3         | 3 2 1 0 |          |       |       |        |       |

| 1  | x                  | x       | x                  | x             | x             | x |          | Invalid                                   |             |         |          |       | 84    | Act -  |       |

| 0  | 0                  | x       | x                  | x             | X             | x | AR       | Address Register                          | w           | 6.7%s   |          |       |       |        |       |

| 0  | 1                  | 0       | 0                  | 0             | 0             | 0 | R0       | Total Number of Characters in Line (*)    | w           |         |          |       |       |        |       |

| 0  | 1                  | 0       | 0                  | 0             | 0             | 1 | R1       | Number of Characters<br>Displayed in Line | w           |         |          |       |       |        |       |

| 0  | 1                  | 0       | 0                  | 0             | 1             | 0 | R2       | Horizontal Sync Position (*)              | w           |         |          |       |       |        |       |

| 0  | 1                  | 0       | 0                  | 0             | 1             | 1 | R3       | Sync Signal Pulse Width                   | w           | V       | 3 V 2    | V1 \  | ′0 НЗ | H2 H   | H0    |

| 0  | 1                  | 0       | 0                  | 1             | 0             | 0 | R4       | Total Number of Lines (*)                 | w           |         |          |       |       |        |       |

| 0  | 1                  | 0       | 0                  | 1             | 0             | 1 | R5       | Total Raster Adjust                       | w           |         |          |       |       |        |       |

| 0  | 1                  | 0       | 0                  | 1             | 1             | 0 | R6       | Number of Lines Displayed                 | w           |         |          |       |       |        |       |

| 0  | 1                  | 0       | 0                  | 1             | 1             | 1 | R7       | Vertical Sync Position (*)                | w           |         |          |       |       |        |       |

| 0  | 1                  | 0       | 1                  | 0             | 0             | 0 | R8       | Scan Mode/Skew                            | w           | С       | 1 C      | DD1   | D0    |        | 11 10 |

| 0  | 1                  | 0       | 1                  | 0             | 0             | 1 | R9       | Maximum Raster Address                    | w           |         |          |       |       |        |       |

| 0  | 1                  | 0       | 1                  | 0             | 1             | 0 | R10      | Cursor Start Raster                       | w           |         | B        | B0    |       |        |       |

| 0  | 1                  | 0       | 1                  | 0             | 1             | 1 | R11      | Cursor End Raster                         | w           |         |          |       |       |        |       |

| 0  | 1                  | 0       | 1                  | 1             | 0             | 0 | R12      | Start Address 1                           | R/W         |         |          |       |       |        |       |

| 0  | 1                  | 0       | 1                  | 1             | 0             | 1 | R13      | Start Address 1                           | n/ <b>v</b> |         |          |       |       |        |       |

| 0  | 1                  | 0       | 1                  | 1             | 1             | 0 | R14      | Cursor                                    | R/W         |         |          |       |       |        |       |

| 0  | 1                  | 0       | 1                  | 1             | 1             | 1 | R15      |                                           | 11/ 11      |         |          |       |       |        |       |

| 0  | 1                  | 1       | 0                  | 0             | 0             | 0 | R16      | Light Pen                                 | R           |         |          |       |       |        |       |

| 0  | 1                  | 1       | 0                  | 0             | 0             | 1 | R17      | Light Fen                                 | n           |         |          |       |       |        |       |

| 0  | 1                  | 1       | 0                  | 0             | 1             | 0 | R18      | Screen 2 Display Start<br>Position (*)    | R/W         |         |          |       |       |        |       |

| 0  | 1                  | 1       | 0                  | 0             | 1             | 1 | R19      | Start Address 2                           | R/W         |         |          |       |       |        |       |

| 0  | 1                  | 1       | 0                  | 1             | 0             | 0 | R20      | Start Address 2                           | n/ W        |         |          |       |       |        |       |

| 0  | 1                  | 1       | 0                  | 1             | 0             | 1 | R21      | Screen 3 Display Start<br>Position (*)    | R/W         |         |          |       |       |        |       |

| 0  | 1                  | 1       | 0                  | 1             | 1             | 0 | R22      | Start Address 3                           | B/W         |         |          |       |       |        |       |

| 0  | 1                  | 1       | 0                  | 1             | 1             | 1 | R23      | Start Address 5                           | F1/ ¥¥      |         |          |       |       |        |       |

| 0  | 1                  | 1       | 1                  | 0             | 0             | 0 | R24      | Screen 4 Display Start<br>Position (*)    | R/W         |         |          |       |       |        |       |

| 0  | 1                  | 1       | 1                  | 0             | 0             | 1 | R25      | Start Address 4                           | B/W         |         |          |       |       |        |       |

| 0  | 1                  | 1       | 1                  | 0             | 1             | 0 | R26      | Start Address 4                           | F1/ VV      |         |          |       |       |        |       |

| 0  | 1                  | 1       | 1                  | 0             | 1             | 1 | R27      | Vertical Sync Position Fine<br>Adjust     | w           |         |          |       |       |        |       |

| 0  | 1                  | 1       | 1                  | 1             | 0             | 0 | R28      | Light Pen Raster                          | R           | DF      | -        |       |       |        |       |

| 0  | 1                  | 1       | 1                  | 1             | 0             | 1 | R29      | Smooth Scroll                             | R/W         |         |          |       |       |        |       |

| 0  | 1                  | 1       | 1                  | 1             | 1             | 0 | R30      | Control                                   | w           | VE      | vs       | IB IL | SYT   | V P1 F | 20    |

| 0  | 1                  | 1       | 1                  | 1             | 1             | 1 | R31      | Control/Status                            | R/W         | SS      | ass      | 2551  | SS0R  | I* E   | SB S  |

\*Note: Values written to these registers are one (1) less than the set values; refer to Notes on operation

#### **Register Description**

#### Address Register (AR)

Sets the number of the internal register. Unchanged until a new value is written.

# Total Number of Characters in Line Register (RO)

Sets horizontal scan sync. Settings indicate number of characters, and are determined by the formula:

Total Number of Characters in Line x Character Period = Horizontal Scan Period

Values written to the register are 1 less than the set values.

#### Number of Characters Displayed in Line Register (R1)

Sets the horizontal display period. Settings indicate number of characters.

#### Horizontal Sync Position Register (R2)

Sets the horizontal sync signal position. Settings indicate number of characters. Values written to the register are 1 less than the set values.

#### Sync Signal Pulse Width Register (R3)

| MSI | 3  |    |    |    |    |    | LSB |  |

|-----|----|----|----|----|----|----|-----|--|

| V3  | V2 | V1 | ٧O | нз | H2 | H1 | H0  |  |

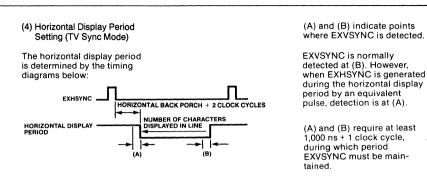

Sets the sync signal pulse width. The 4 high-order bits are used for the vertical sync signal, the 4 low-order bits for the horizontal sync signal. the TV sync mode, the 4 low-order bits are used as the horizontal back porch.

# Total Number of Lines Register (R4)

Used the the total raster adjust register to set vertical sync (field sync is set by number of rasters). Setting is in number of lines. Values written to the register are 1 less than the set value.

# Total Raster Adjust Register (R5)

Used to fine tune the vertical sync. Settings indicate number of rasters, and must be less than the maximum raster address. Vertical sync is determined by the formula:

Vertical Sync = Total Number of Lines x Maximum Raster Address + Total Raster Adjust

#### Number of Lines Displayed Register (R6)

Sets the vertical display period. Settings indicate number of lines.

#### Vertical Sync Position Register (R7)

Used with the vertical sync position fine adjust register (R27) to set vertical sync position using raster count. Settings indicate number of lines. Values written to the register are 1 less than the set values.

#### Scan Mode/Skew Register (R8)

| MSE | 3  |    |    | 1. | 1  | LSB |  |

|-----|----|----|----|----|----|-----|--|

| C1  | C0 | D1 | D0 |    | 11 | 10  |  |

Sets cursor display signal and display timing signal skew, and the scan mode. Bit functions are as shown below:

#### C1 C0 CUDISP Output

| 0  | 0 | Output without skew      |

|----|---|--------------------------|

| 0  | 1 | Skewed by 1<br>character |

| 1. | 0 | Skewed by 2 characters   |

| 1  | 1 | No CUDISP output         |

#### D1 D0 DISPTMG Output

| 0 | 0 | Output without skew      |

|---|---|--------------------------|

| 0 | 1 | Skewed by 1<br>character |

| 1 | 0 | Skewed by 2 characters   |

| 1 | 1 | No DISPTMG output        |

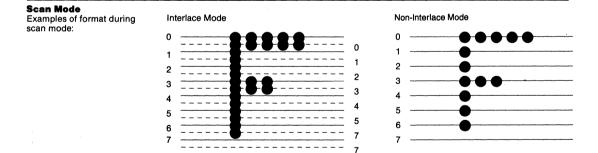

#### I1 IO Scan Mode

| 0 | 0 | Non-interlace mode       |

|---|---|--------------------------|

| 0 | 1 | Interlace mode           |

| 1 | 0 | Non-interlace mode       |

| 1 | 1 | Interlace and video mode |

#### Maximum Raster Address Register (R9)

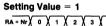

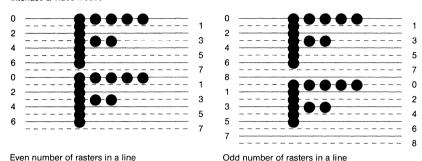

Sets the number of rasters in a line. In interlace and noninterlace modes, the value written is 1 less than the set value; in interlace and video mode, 2 less. Examples of settings in each mode are as follows:

#### Interlace mode

| Ω. |       |

|----|-------|

|    | <br>0 |

| 1  | <br>  |

|    |       |

| _  | <br>2 |

| 3  | <br>_ |

| 4  |       |

|    |       |

Raster count - 5 Value written - 4

#### Non-interlace mode

| 0 |  |

|---|--|

| 1 |  |

| 2 |  |

| 3 |  |

|   |  |

Raster count - 5 Value written - 4

Interlace & video modes

| • |  |  |  |  |  |  |  | _ | 1 |

|---|--|--|--|--|--|--|--|---|---|

|   |  |  |  |  |  |  |  |   | _ |

|   |  |  |  |  |  |  |  |   | 3 |

|   |  |  |  |  |  |  |  |   |   |

Raster count - 5 Value written - 3

Non-interlace mode and Interlace mode: Written value = Setting value -1 Interlace mode & video mode: Written value = Setting value -2

#### **Register Description**

(Continued)

#### Cursor Start Raster Register (R10)

| MSB |    |  | I | LSB |  |

|-----|----|--|---|-----|--|

| B1  | BO |  |   |     |  |

Sets the cursor display mode and the display start raster. Settings indicate number of rasters. Cursor display mode bit function is as follows:

#### Cursor Display B1 B0 Mode

| 0 | 0 | Displays without<br>blinking |

|---|---|------------------------------|

| 0 | 1 | No display                   |

| 1 | 0 | Blinks in 16-field<br>sync   |

| 1 | 1 | Blinks in 32-field sync      |

#### Cursor End Raster Register (R11)

Sets the cursor display end raster. Settings indicate number of rasters.

#### Start Address Registers (R12, R13, R19, R20, R22, R23, R25, R26)

Four sets of 14-bit paired registers used to set the starting memory address for screen display that enable independent paging/scrolling when screen is partitioned. Registers are for Start Address 1 (R12, R13), Start Address 2 (R19, R20), Start Address 3 (R22, R23) and Start Address 4 (R25, R26).

#### Cursor Registers (R14, R15)

14-bit paired registers used to set the cursor display memory address.

#### Light Pen Registers (R16, R17)

14-bit paired registers to which the memory address is written when the light pen strobe signal goes high. Memory address value must be compensated in software for delay in the light pen detection circuit.

# Light Pen Raster Register (R28)

| MSB L | -5 |

|-------|----|

| DP    |    |

Register to which the raster address and display status bit are written when the light pen strobe signal goes high. When the light pen register or light pen raster register are written to during the display period, the display status bit is set to 1; during blank period, reset to 0.

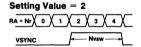

#### Vertical Sync Position Fine Adjust Register (R27)

Used to fine-tune the vertical sync signal within the line set by the vertical sync position register. Settings indicate number of rasters. Examples of settings are shown below:

Setting 0 must not be written as it will cause the control register to disable the vertical sync position adjust register, resulting in a vertical sync signal output of RA = 0. The set value must be less than the maximum raster address.

#### Display Start Position Registers (R18, R21, R24)

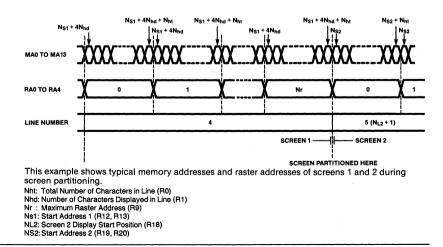

Sets the starting line numbers for display start addresses 2, 3, and 4 when screen is partitioned. See following figure. Values written to the register are 1 less than the line number; 0 must not be written. Examples of settings are shown below:

#### Line Number Display Screen

| 0<br>1<br>2      | Screen 1<br>(Start address 1)                 |

|------------------|-----------------------------------------------|

| 3                | Screen 2<br>(Start address 2,<br>Register 18) |

| 4<br>5<br>6<br>7 | Screen 3<br>(Start address 3,<br>Register 21) |

| 8<br>9           | Screen 4<br>(Start address 4,<br>Register 24) |

|                  |                                               |

Value written for start position 2 = 2 Value written for start position 3 = 3 Value written for start position 4 = 7

#### Smooth Scroll Register (R29)

Sets the starting raster address within a line. Setting indicates number of rasters. Smooth scrolling can be used in interlace and non-interlace modes only.

Settings are valid for screens specified by SS3 to SS0 of the control/status register. Settings must be less than the maximum raster address. Examples of settings are shown below:

### **Register Description**

(Continued)

#### Control Register (R30)

| MS | 3  |    |    |    |    |    | LSB |

|----|----|----|----|----|----|----|-----|

| VE | vs | IB | IL | SY | тν | P1 | P0  |

#### Controls the external sync function, interrupt function, vertical sync position fine adjust function and screen

partition function. This register must be initialized by software after reset is released. Bit functions are as shown below:

#### VE VS TV External Sync Function

| 0 | 0 | 0 | Both VSYNC and HSYNC are in output mode. DISPTMG is active. External<br>sync operation is disabled.                                                                                                         |

|---|---|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 1 | 0 | Outputs VSYNC for odd-numbered fields only in interlace mode. No VSYNC<br>output when the programmed values of max. raster address and vertical<br>sync position are odd numbers in interlace & video mode. |

| 1 | 0 | 0 | EXVSYNC is in input mode but external sync signal ignored. DISPTMG is<br>active.                                                                                                                            |

| 1 | 1 | 0 | EXVSYNC is in input mode and external sync signal is accepted. DISPTMG<br>goes low (disabled).                                                                                                              |

| 0 | 0 | 1 | Disallowed                                                                                                                                                                                                  |

| 0 | 1 | 1 | Disallowed                                                                                                                                                                                                  |

| 1 | 0 | 1 | Both EXVSYNC and EXHSYNC are in input mode and external sync signal is<br>accepted. DISPTMG output is active.                                                                                               |

| 1 | 1 | 1 | Both EXVSYNC and EXHSYNC are in input mode and external sync<br>signal is accepted. DISPTMG goes low (disabled).                                                                                            |

|   |   |   |                                                                                                                                                                                                             |

#### Notes:

1. When VS = 1, DISPTMG goes low.

2. When TV = 0, indicates master-slave mode. When TV = 1, indicates TV sync mode.

3. In TV sync mode, the horizontal back porch must be set using the horizontal sync pulse

width register. 4. In TV sync mode, the internal control is in non-interlace mode.

#### IR IL Interrupt Function

| 0 | 0 | None                                |  |

|---|---|-------------------------------------|--|

| 0 | 1 | With light pen strobe               |  |

| 1 | 0 | With vertical blanking              |  |

| 1 | 1 | With light pen or vertical blanking |  |

Note: Interrupt signal is output for CUDISP while DISPTMG is low.

| SY | Vertical Sync Position Fine Adjust Function          |  |

|----|------------------------------------------------------|--|

| 0  | Vertical sync position fine adjust register disabled |  |

| 1  | Vertical sync position fine adjust register enabled  |  |

| <b>P1</b> | PO | Screen Partition Function                                                     |

|-----------|----|-------------------------------------------------------------------------------|

| 0         | 0  | Start Address 1 enabled                                                       |

| 0         | 1  | Start addresses 1 and 2 enabled; screen partitioned into two sections         |

| 1         | 0  | Start addresses 1, 2, and 3 enabled; screen partitioned into three sections   |

| 1         | 1  | Start addresses 1, 2, 3, and 4 enabled; screen partitioned into four sections |

Note: Screen address 1 is always displayed starting from line number 0.

#### **Register Description**

(Continued)

## Control/Status Register (R31)

Controls the smooth scrolling and raster interpolation functions, and performs read/write of the status register. This register must be initialized by software after reset is released. Control bit functions are as follows:

| Control Bits | Function                                                                                                                                                                                                                                                                                                                                                             |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SS3 to SS0   | Smooth scrolling control bits; when set to 1 the smooth scrolling register is<br>enabled. Bits correspond to the screens as follows:<br>SS3 = screen 4<br>SS2 = screen 3<br>SS1 = screen 2<br>SS0 = screen 1                                                                                                                                                         |

| RI           | Raster interpolation bit. Set to 1, raster interpolation is performed. The raster<br>counter is incremented every two rasters, doubling the vertical sync rate.<br>Therefore, in this case, registers related to vertical sync control must be<br>reprogrammed. The raster interpolation function can't be used in external sync<br>mode and interlace & video mode. |

Notes: 1. "0s" must be written to lower 3 bits of the control register.

2. Refer to diagram of "Double-Size Vertical Display" and item 6 of Notes on Operation.

#### **Status Bits**

The functions of status bits are as follows:

| E | Display Field Status                                  |  |

|---|-------------------------------------------------------|--|

| 0 | Odd-numbered screen display, or in non-interlace mode |  |

| 1 | Even-numbered screen display                          |  |

#### SB **Vertical Blanking Status**

| 0 | During screen display    |  |

|---|--------------------------|--|

| 1 | During vertical blanking |  |

#### SL **Light Pen Strobe Status**

| 0 | Light pen strobe ignored  |      |

|---|---------------------------|------|

| 1 | Light pen strobe accepted | <br> |

#### Notes:

1. Light pen strobe status is cleared by reset or by read of the status register.

2. Vertical blanking status and light pen strobe status are set regardless of the setting of the control register interrupt function.

3. E bit is controlled by the vertical blank. Therefore, E bit status is different from normal field image, and it's update timing changes depending on number of lines displayed. To get correct status, E bit must be read immediately after the display period.

#### **Restrictions on Values** Written to Registers Values which may be written to internal registers are as follows: < number of characters (B1) < total number of characters in line (R0) $+ 1 \le 256$ 0 (1) displayed in line (2) 0 < number of lines displayed (R6) < total number of lines (R4) $+1 \le 128$ (3) 0 $\leq$ horizontal sync position (R2) $\leq$ total number of characters in line (R0) (4) 0 $\leq$ vertical sync position (R7) $\leq$ total number of lines (R4) (5) 0 $\leq$ cursor start raster (R10) $\leq$ cursor end raster (R11) $\leq$ maximum raster address (R9) (interlace mode and non-interlace modes) $\leq$ cursor start raster (R10) $\leq$ cursor end raster (R11) $\leq$ maximum raster address (R9)+ 1 0 (interlace & video mode) (6) 2 $\leq$ maximum raster address (R9) $\leq$ 30 (interlace & video mode only) (7) 3 $\leq$ total number of characters in line (R0) (except in non-interlace mode) 5 ≤ total number of characters in line (R0) (non-interlace mode only) (8) Vertical sync position fine adjust (R27) < maximum raster address (R9) (9) Smooth scroll (R29) < maximum raster address (R9)

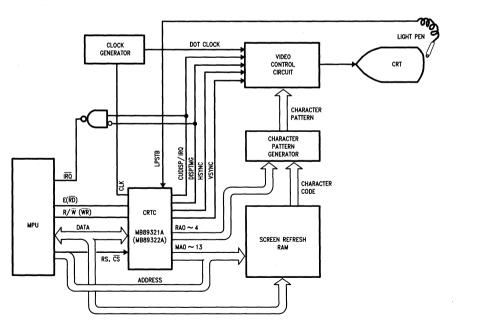

#### System Block Diagram

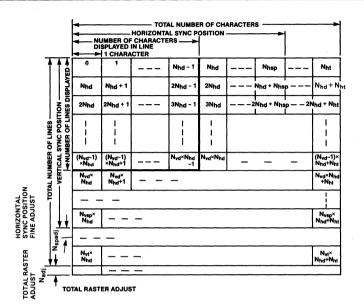

### **Programmable Values**

Programmable values which can be written to registers and their respective symbols are as shown below:

| Register<br>Number | Register Name                          | Programmable Value | Symbol              |

|--------------------|----------------------------------------|--------------------|---------------------|

| R0                 | Total Number of Characters in Line     | Characters         | Nht                 |

| R1                 | Number of Characters Displayed in Line | Characters         | Nhd                 |

| R2                 | Horizontal Sync Position               | Characters         | Nhsp                |

| R3                 | Sync Signal Pulse Width                | Rasters/Characters | Nvsw/Nhsw           |

| R4                 | Total Number of Lines                  | Lines              | Nvt                 |

| R5                 | Total Raster Adjust                    | Rasters            | Nadj                |

| R6                 | Number of Lines Displayed              | Lines              | Nvd                 |

| R7                 | Vertical Sync Position                 | Lines              | Nvsp                |

| R8                 | Scan Mode/Skew                         |                    |                     |

| R9                 | Maximum Raster Address                 | Rasters            | Nr                  |

| R10                | Cursor Start Raster                    | Rasters            | N <sub>CSTART</sub> |

| R11                | Cursor End Raster                      | Rasters            | N <sub>CEND</sub>   |

| R12                | Start Address 1                        |                    | N                   |

| R13                | Start Address 1                        |                    | N <sub>SI</sub>     |

| R14                | Cursor                                 |                    |                     |

| R15                | Cursor                                 |                    |                     |

| R16                | Light Pen                              |                    |                     |

| R17                | Light Fell                             |                    |                     |

| R18                | Screen 2 Display Start Position        | Lines              | N <sub>L2</sub>     |

| R19                | Start Address 2                        |                    | N                   |

| R20                |                                        |                    | N <sub>S2</sub>     |

| R21                | Screen 3 Display Start Position        | Lines              | N <sub>L3</sub>     |

| R22                | Start Address 3                        |                    | N.                  |

| R23                | Start Address 5                        |                    | N <sub>S3</sub>     |

| R24                | Screen 4 Display Start Position        | Lines              | N <sub>L4</sub>     |

| R25                | Start Address 4                        |                    | N <sub>S4</sub>     |

| R26                | Start Address 4                        |                    | NS4                 |

| R27                | Vertical Sync Position Fine Adjust     | Rasters            | Nspadj              |

| R28                | Light Pen Raster                       |                    |                     |

| R29                | Smooth Scroll                          | Rasters            | Nradj               |

| R30                | Control                                |                    |                     |

| R31                | Control/Status                         |                    |                     |

|                    |                                        |                    |                     |

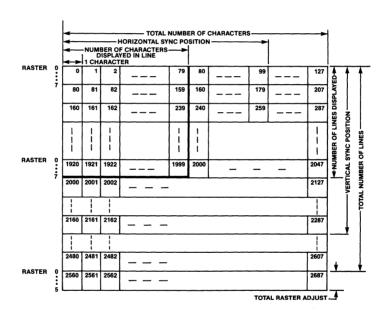

#### **Screen Format**

Line numbers are counted starting at the following addresses:

Line number 0 = starts from memory address 0 Line number 1 = starts from memory address Nhd Line number 2 = starts from memory address 2Nhd

### Example of Screen Format

| Dot clock rate       | 16.128 MHz |

|----------------------|------------|

| Horizontal frequency | 15.75 kHz  |

| Vertical frequency   | 60.1145 Hz |

At the following clock rates and register settings, the screen format is as shown in the diagrams below:

| Total number of characters in line, Register 0:     | 127 |

|-----------------------------------------------------|-----|

| Number of characters displayed in line, Register 1: | 80  |

| Horizontal sync position, Register 2:               | 99  |

| Sync signal pulse width, Register 3:                | 8   |

| Total number of lines, Register 4:                  | 31  |

| Total raster adjust, Register 5:                    | 6   |

| Number of lines displayed, Register 6:              | 25  |

| Vertical sync position, Register 7:                 | 27  |

| Maximum raster address, Register 9:                 | 8   |

4

٠

## Scan Mode

(Continued)

#### Interlace & Video Modes

Even number of rasters in a line

Examples of settings for the cursor start and end raster registers:

End address = 6

End address = 4

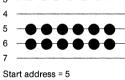

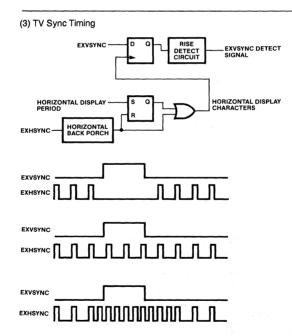

## TV Sync Mode

Example of a TV Sync mode circuit:

TV sync mode is used to superimpose displays on TV or video signals. In the above example a 1/n fOSC dot shift

will occur. Accordingly, an appropriate prescaler should be designed to avoid image resolution problems.

During HSYNC, CLK must be low (stopped).

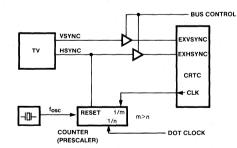

Master-slavemode is used to synchronize master and slave CRT controllers. The screen formats and clock phases of the two CRTCs must match.

Since HSYNC is output, PLL can be used.

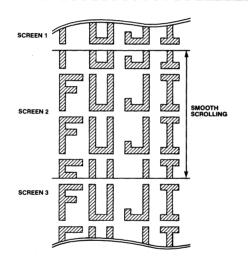

#### Smooth Scroll

Example of smooth scrolling display:

In the example, screen 2 is being smooth scrolled.

#### Double-Size Vertical Display

6

Without raster interpolation function

With raster interpolation function

The vertical size of the display can be doubled using the raster interpolation function as shown in the example.

In raster interpolation, the raster address is updated every second raster.

Refer to item 6 of Notes on Operation.

#### Absolute Maximum Ratings

| Parameter                     | Symbol           | Rating       | Unit |

|-------------------------------|------------------|--------------|------|

| Input Voltage                 | V <sub>IN</sub>  | -0.3 to +7.0 | v    |

| Supply Voltage                | Vcc              | -0.3 to +7.0 | V    |

| Operating Ambient Temperature | TA               | -40 to +85   | °C   |

| Storage Temperature           | T <sub>STG</sub> | -55 to +150  | °C   |

| Power Dissipation             | PD               | 600          | mW   |

|                               |                  |              |      |

**Note:** Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Recommended Operating Conditions

|                     |              |                  | Value |      |                 |      |

|---------------------|--------------|------------------|-------|------|-----------------|------|

| Parameter           |              | Symbol           | Min.  | Тур. | Max.            | Unit |

| Supply Voltage      |              | V <sub>CC</sub>  | 4.5   | 5.0  | 5.5             | ٧    |

| Cuppiy Vollage      |              | V <sub>SS</sub>  |       | 0.0  |                 | ٧    |

| Input High Voltage  | LPSTB, CLK   | V <sub>IH1</sub> | 2.2   |      | V <sub>CC</sub> | ٧    |

| input high voltage  | Other Inputs | VIH              | 2.0   |      | V <sub>CC</sub> | ٧    |

| Input Low Voltage   | LPSTB, CLK   | V <sub>IL1</sub> | -0.3  |      | 0.6             | ٧    |

| input Low Voltage   | Other inputs | VIL              | -0.3  |      | 0.8             | ٧    |

| Ambient Temperature |              | TA               | -20   | 25   | + 75            | °C   |

|                     |              |                  |       |      |                 |      |

#### **DC Characteristics**

Recommended operating conditions unless otherwise noted.

|                          |                                  |                  |                                                     | Value |     |      |      |

|--------------------------|----------------------------------|------------------|-----------------------------------------------------|-------|-----|------|------|

| Parameter                |                                  | Symbol           | <b>Test Conditions</b>                              | Min   | Тур | Max  | Unit |

| Input High               | LPSTB, CLK                       | V <sub>IH1</sub> |                                                     | 2.2   |     | Vcc  | V    |

| Voltage                  | Other Inputs                     | VIH              |                                                     | 2.0   |     | Vcc  | V    |

| Input Low                | LPSTB,CLK                        | VIL1             |                                                     | -0.3  |     | 0.6  | V    |

| Voltage                  | Other Inputs                     | VIL              |                                                     | -0.3  |     | 0.8  | V    |

| Input Leakage<br>Current | D0 to D7,<br>EXHSYNC,<br>EXVSYNC | IIL              | $V_{IN=0.4 V \text{ to } 2.4 V,}$<br>$V_{CC}=5.5 V$ | -10   |     | 10   | μΑ   |

|                          | Other<br>Inputs                  | I <sub>IL1</sub> | $V_{IN} = 0 V \text{ to } 5.5 V$                    | -2.5  |     | 2.5  | μΑ   |

| Output High              | D0 to D7                         | VOH              | I <sub>OH</sub> =-205 μA                            | 2.4   |     |      | V    |

| Voltage                  | Other<br>Outputs                 | V <sub>OH1</sub> | I <sub>OH</sub> =-100 μA                            | 2.4   |     |      | v    |

| Output Low               | Voltage                          | VOL              | I <sub>OL</sub> =1.6 mA                             |       |     | 0.4  | ٧    |

| Input<br>Capacitance     | D0 to D7,<br>EXHSYNC,<br>EXVSYNC | C <sub>IN</sub>  | V <sub>IN</sub> =0 V                                |       |     | 12.5 | pF   |

|                          | Other<br>Outputs                 | C <sub>IN1</sub> | f=1.0 MHz                                           |       |     | 10.0 | pF   |

| Ouput Capacitance        |                                  | COUT             |                                                     |       |     | 10.0 | pF   |

| Power Dissipation        |                                  | PD               | V <sub>CC</sub> =V <sub>max</sub><br>f=1.0 MHz      |       | 10  | 30   | mW   |

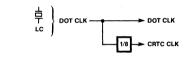

AC Characteristics Recommended operating conditions unless otherwise noted.

|                      |                                                      |                                           |              | Value         | •    |      |     |

|----------------------|------------------------------------------------------|-------------------------------------------|--------------|---------------|------|------|-----|

| Paramete             | er                                                   | Symbol                                    | Conditions   | Min.          | Typ. | Max. | Uni |

|                      | Clock Period                                         | t <sub>CLK</sub>                          |              | 250           |      |      | ns  |

|                      | Clock High                                           | t <sub>PWCH</sub>                         |              | 100           |      |      | ns  |

|                      | Clock Low                                            | tPWCL                                     |              | 100           |      |      | ns  |

|                      | Clock Rise                                           | t <sub>CR</sub>                           |              |               |      | 20   | ns  |

|                      | Clock Fall                                           | t <sub>CF</sub>                           |              |               |      | 20   | ns  |

| CRT                  | Memory Address Delay                                 | t <sub>MAD</sub>                          | . (1)        |               |      | 80   | ns  |

| Controller           | Raster Address Delay                                 | t <sub>RAD</sub>                          | - (1) -      |               |      | 100  | ns  |

|                      | Display Timing Delay                                 | t <sub>DTD</sub>                          |              |               |      | 120  | ns  |

|                      | Cursor Timing Delay                                  | t <sub>CDD</sub>                          |              |               |      | 120  | ns  |

|                      | Horizontal Synchronous<br>Delay                      | t <sub>HSD</sub>                          |              |               |      | 100  | ns  |

|                      | Vertical Synchronous Delay                           | t <sub>VSD</sub>                          |              |               |      | 120  | ns  |

|                      | Clock Stop                                           | t <sub>CLKST</sub>                        | _            | 100           |      |      | ns  |

|                      | External Horizontal<br>Synchronous Signal Width      | t <sub>PWHS</sub>                         |              | 1000          |      |      | ns  |

|                      | External Horizontal<br>Synchronous Rise              | t <sub>HR</sub>                           |              |               |      | 20   | ns  |

| External<br>Synchro- | External Horizontal<br>Synchronous Fall              | t <sub>HF</sub>                           |              |               | . '  | 20   | ns  |

| nization             | External Vertical *1<br>Synchronous Signal Width     | t <sub>PWVS</sub> /<br>t <sub>PWVSS</sub> | - (2)        | 1220/<br>1750 |      |      | ns  |

|                      | External Vertical<br>Synchronous Rise                | t <sub>VR</sub>                           |              |               |      | 20   | ns  |

|                      | External Vertical<br>Synchronous Fall                | t <sub>VF</sub>                           |              |               |      | 20   | ns  |

|                      | External Synchronous<br>Setup<br>(Master-slave mode) | tvss                                      |              | 50            | -    |      | ns  |

|                      | Light Pen Strobe Width                               | t <sub>PWLP</sub>                         |              | 60            |      |      | ns  |

| Light<br>Pen         | Light Pen Strobe                                     | t <sub>LPDR</sub>                         | _ (3)        |               |      | 0    | ns  |

|                      | Maximum Period                                       | tLPDF                                     |              |               |      | 70   | ns  |

|                      | Enable Period                                        | t <sub>E</sub>                            |              | 0.5           |      |      | μs  |

|                      | Enable High                                          | t <sub>PWEH</sub>                         |              | 0.22          |      |      | μs  |

|                      | Enable Low                                           |                                           |              | 0.21          |      |      | μs  |

|                      | Enable Rise                                          | t <sub>ER</sub>                           |              |               |      | 20   | ns  |

| CRT                  | Enable Fall                                          | t <sub>EF</sub>                           | [(4) MB89321 |               |      | 20   | ns  |

| Interface            | Address Setup                                        | t <sub>AS</sub>                           | only]        | 40            |      |      | ns  |

| 1                    | Data Delay                                           | t <sub>DDR</sub>                          |              |               |      | 120  | ns  |

|                      | Data Access                                          | t <sub>ACC</sub>                          |              |               |      | 160  | ns  |

|                      | Address Hold                                         | t <sub>AH</sub>                           |              | 10            |      |      | ns  |

|                      | Data Hold                                            | t <sub>H</sub>                            |              | 10            |      |      | ns  |

|                      | Data Setup                                           | t <sub>DSW</sub>                          |              | 60            |      |      | ns  |

**AC Characteristics** (Continued)

|                  |                     |                   |              | Value | Ð   |                             |    |

|------------------|---------------------|-------------------|--------------|-------|-----|-----------------------------|----|

| Paramet          | er                  | Symbol            | Conditions   | Min   | Тур | Max                         | Un |

|                  | Read Address Setup  | t <sub>AR</sub>   |              | 0     |     |                             | ns |

|                  | Read Low            | t <sub>RR</sub>   |              | 160   |     |                             | ns |

|                  | Read Address Hold   | t <sub>RA</sub>   |              | 0     |     |                             | ns |

|                  | Write Address Setup | t <sub>AW</sub>   |              | 0     |     |                             | ns |

|                  | Write Low           | t <sub>WW</sub>   | [(5)MB89322A | 190   |     |                             | ns |

| CPU<br>Interface | Write Address Hold  | t <sub>WA</sub>   | only] -      | 0     |     |                             | ns |

| 2                | Data Delay          | t <sub>RD</sub>   |              |       |     | 120                         | ns |

|                  | Data Hold           | t <sub>DF</sub>   |              | 10    |     |                             | ns |

|                  | Data Setup          | t <sub>DW</sub>   |              | 60    |     |                             | ns |

|                  | Data Hold           | t <sub>WD</sub>   |              | 0     |     |                             | ns |

|                  | Access Inhibit      | t <sub>DIS</sub>  |              | 210   |     |                             | ns |

|                  | Interrupt Delay     | t <sub>IRDF</sub> |              |       |     | 150                         | ns |

| IRQ              | Interrupt Delay *2  | t <sub>IRDR</sub> | (6)          |       |     | 1/2t <sub>clk</sub><br>+150 | ns |

Note:

\*1. External vertical synchronous signal width t<sub>pWVS</sub> = 1000 ns + t<sub>CLK</sub> (TV sync mode) t<sub>PWVSS</sub> = 1000 ns + 3 t<sub>CLK</sub> (Master slave mode)

\*2. Rising delay time when light pen strobe input in non display time

P/S SHIFT REGISTER

PRESCALER 1/8

CLK

> VIDEO

Clock

CLOCK

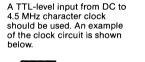

TTL-LEVEL-INPUT

A circuit example for horizontal 8-dot character mode is as follows:

(1) CRT Controller

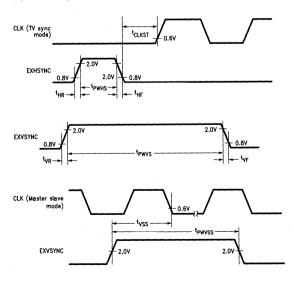

(2) External synchronization

••

FUJITSU

4

(Continued)

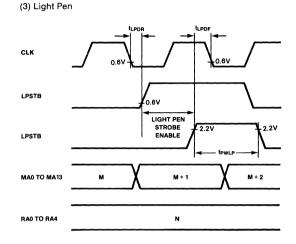

When the light pen strobe is enabled, LPSTB goes high, M+2 is loaded into the light pen register, N into the light pen raster register, and the display status bit is set.

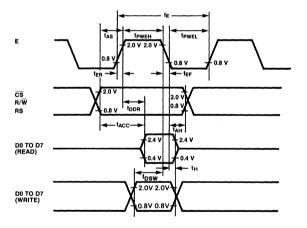

(4) CPU Interface 1 (MB89321A only)

FUJITSU

#### Timing Diagrams (Continued)

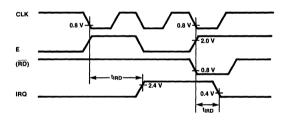

(5) CPU Interface 2 (MB89322A only)

(6) IRQ Timing

**Notes on Operation**

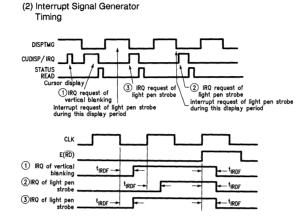

(1) Screen Partition Timing

4

FUJITSU

#### Notes on Operation (Continued)

The interrupt signal is output to the CUDISP pin during display blanking. The interrupt signal can be generated as shown in the diagram below.

When the cursor is not enabled, the CUDISP pin functions as IRQ.

In TV sync mode, EXHSYNC is enabled when a pulse of 1,000 ns or more is applied. Also, during vertical blanking, EXVSYNC is enabled to sync the controller's internal horizontal display period signal. In order to use the TV sync function, a horizontal display period should be set. The basic circuit required to do this is shown to the left.

Note: Low (enabled) during the horizontal display period.

The TV sync function may not operate under the timing shown here at the immediate left.

The TV sync function is activated using the timing as shown here.

#### **Notes on Operation**

(Continued)

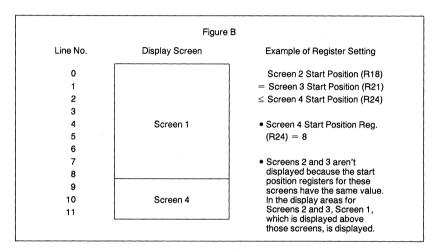

#### (5) Screen Partitioning

The display order of partitioned screens can be changed by programming the start position registers (R18, R21, and R24) for each partitioned screen, except screen 1, which is always displayed from line 0 on the screen. (See Figure A below.)

But, when the same values are programmed to the start position registers, the partitioned screens for those start position registers aren't displayed, even if those partitioned screens are enabled by P0 and P1 bits.

|          | Figure         | A                                                |

|----------|----------------|--------------------------------------------------|

| Line No. | Display Screen | Example of Register Setting                      |

| 0        |                | Screen 3 Start Position (R21)                    |

| 1        | Screen 1       | $\leq$ Screen 2 Start Position (R18)             |

| 2        |                | $\leq$ Screen 4 Start Position (R24)             |

| 3        |                |                                                  |

| 4        | Screen 3       | <ul> <li>Screen 2 Start Position Reg.</li> </ul> |

| 5        |                | (R18) = 5                                        |

| 6        |                | <ul> <li>Screen 3 Start Position Reg.</li> </ul> |

| 7        | Screen 2       | (R21) = 2                                        |

| 8        |                | <ul> <li>Screen 4 Start Position Reg.</li> </ul> |

| 9        |                | (R24) = 8                                        |

| 10       | Screen 4       |                                                  |

| 11       |                |                                                  |

4

# Notes on Operation (Continued)

#### (6) Raster Interpolation

At present, two versions of MB89321A/89322A are provided: One has the raster interpolation function, and another has no raster interpolation function. On MB89321A/89322A without the raster interpolation function, "0" must always be written to RI bit of the control/status register (R31).

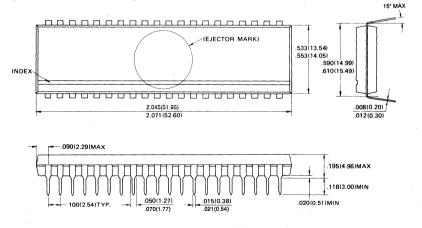

#### Package Dimensions Dimensions in inches (millimeters)

#### 40-Lead Plastic Dual In-Line Package (Case No.: DIP-40P-M01)

© 1985 FUJITSU LIMITED D40005S-1C

FUJITSU