PSG

The Programmable Sound Generator (PSG) is a sound chip designed by General Instrument (GI) in 1978. The specific model used in the CPC is the AY-3-8912 chip.

The PSG is able to output three separate sound channels (named Channel A, B and C). Each channel can be used to output tones and/or white noise.

Contents

- 1 PSG Part numbers used in the CPC during its lifetime

- 2 I/O Access

- 3 PSG Registers

- 3.1 00h - Channel A Tone Frequency Low (8bit)

- 3.2 01h - Channel A Tone Frequency High (4bit)

- 3.3 02h - Channel B Tone Frequency Low (8bit)

- 3.4 03h - Channel B Tone Frequency High (4bit)

- 3.5 04h - Channel C Tone Frequency Low (8bit)

- 3.6 05h - Channel C Tone Frequency High (4bit)

- 3.7 06h - Noise Frequency (5bit)

- 3.8 07h - Mixer Control Register

- 3.9 08h - Channel A Volume (0-0Fh=volume, 10h=use envelope instead)

- 3.10 09h - Channel B Volume (0-0Fh=volume, 10h=use envelope instead)

- 3.11 0Ah - Channel C Volume (0-0Fh=volume, 10h=use envelope instead)

- 3.12 0Bh - Volume Envelope Frequency Low (8bit)

- 3.13 0Ch - Volume Envelope Frequency High (8bit)

- 3.14 0Dh - Volume Envelope Shape (4bit)

- 3.15 0Eh - External Dataregister Port A

- 3.16 0Fh - External Dataregister Port B

- 4 Noise Generator

- 5 D/A converter table

- 6 Mono and Stereo Output

- 7 BASIC Sound Test

- 8 Block Diagram

- 9 Schematics

- 10 Chip Variants

- 11 Datasheets

- 12 Links

PSG Part numbers used in the CPC during its lifetime

I/O Access

The PSG has 16 read/writeable data registers, and a write-only index register. Only the 4 least significant bits of the selected register number are considered.

Both the index and data registers are accessed through PPI Port A, depending on the current setting of the BC1 and BDIR bits in PPI Port C. The four possible combinations are:

| PPI Port C | BDIR | BC1 | Function |

|---|---|---|---|

| 00xxxxxx | 0 | 0 | Inactive |

| 01xxxxxx | 0 | 1 | Read from selected PSG register |

| 10xxxxxx | 1 | 0 | Write to selected PSG register |

| 11xxxxxx | 1 | 1 | Select PSG register |

The procedure to write data to a specific PSG register from the PPI is quite tedious. It consists of the following steps:

- Write the register number to PPI Port A

- set BC1/BDIR to Select Register

- and back to Inactive

- Now write the data to PPI Port A

- set BC1/BDIR to Write Data

- and back to Inactive.

Consult this article for more information: How to access the PSG via PPI

PSG Registers

00h - Channel A Tone Frequency Low (8bit)

01h - Channel A Tone Frequency High (4bit)

02h - Channel B Tone Frequency Low (8bit)

03h - Channel B Tone Frequency High (4bit)

04h - Channel C Tone Frequency Low (8bit)

05h - Channel C Tone Frequency High (4bit)

The tone (square wave) frequency in Hertz is calculated as follows:

F = 1MHz / 16 / nn ;with nn in range 1..4095 (nn=0 acts as nn=1)

Possible frequencies are in range from 62500Hz (nn=1) down to approx. 15.26Hz (nn=4095).

06h - Noise Frequency (5bit)

The noise frequency in Hertz is calculated as follows:

F = 1MHz / 16 / nn ;with nn in range 1..31 (nn=0 acts as nn=1)

Noise can be output on all 3 channels, but there is only one noise generator (so all channels share the same noise frequency). The noise generator consists of 17bit shift register, and a 1bit noise level (0=LOW or 1=HIGH). These are updated at the selected frequency as follows:

noise_level = noise_level XOR shiftreg.bit0 newbit = shiftreg.bit0 XOR shiftreg.bit3 shiftreg = (shiftreg SHR 1) + (newbit SHL 16)

Note that level isn't set equal to bit0, instead, it toggles when bit0=1.

07h - Mixer Control Register

The control register enables or disables the sound channels. Each channel can output a Tone and/or Noise.

Bit 0 Channel A Tone (1=off, 0=on) Bit 1 Channel B Tone (1=off, 0=on) Bit 2 Channel C Tone (1=off, 0=on) Bit 3 Channel A Noise (1=off, 0=on) Bit 4 Channel B Noise (1=off, 0=on) Bit 5 Channel C Noise (1=off, 0=on) Bit 6 Port A Direction (1=output, 0=input) (should be always 0 for CPC) Bit 7 Port B Direction (1=output, 0=input) (not used in CPC)

If both Tone and Noise are disabled on a channel, then a constant HIGH level is output (useful for digitized speech). If both Tone and Noise are enabled on the same channel, then the signals are ANDed (the signals aren't ADDed) (ie. HIGH is output only if both are HIGH).

08h - Channel A Volume (0-0Fh=volume, 10h=use envelope instead)

09h - Channel B Volume (0-0Fh=volume, 10h=use envelope instead)

0Ah - Channel C Volume (0-0Fh=volume, 10h=use envelope instead)

Defines the volume, 0=off, 15=max. If bit4=1, then the volume is taken from the envelope generator. The volume is non-linear. Below formula does comply with the PSG datasheet, and does more or less match the voltages measured on the CPCs speaker (the voltages on the CPCs stereo connector seem to be slightly different though).

amplitude = max / sqrt(2)^(15-nn) eg. 15 --> max/1, 14 --> max/1.414, 13 --> max/2, etc.

The volume affects only HIGH levels. LOW levels are always NULL. Ie. sound output toggles between +VOL and NULL (not between +VOL and -VOL).

Digitized samples can be written to the volume registers (mind that volume is non-linear). When doing that, it's best to switch the channel to constant HIGH level (by disabling both Tone and Noise). Another method would be to set tone frequency to 000h or 001h (the resulting frequency is too high to be audible, so the HIGH/LOW levels sound like a constant HALF level).

0Bh - Volume Envelope Frequency Low (8bit)

0Ch - Volume Envelope Frequency High (8bit)

Envelope step frequency (tone or noise) calculated as follows:

F = 1MHz / 16 / nn ;with nn in range 1..65535 (nn=0 acts as nn=1)

Depending on the envelope shape, the volume is incremented from 0 to 15, or decremented from 15 to 0. In either case it takes 16 steps to complete, the completion time for 16 steps is therefore:

T = nn*256 / 1MHz ;with nn in range 1..65535 (256us .. 16.7 seconds)

0Dh - Volume Envelope Shape (4bit)

The written value specifies the envelope shape, the four bits have the following meaning:

Bit 0 Hold (1=stop envelope past first cycle) Bit 1 Alternate (1=reverse direction at end of each cycle) Bit 2 Attack (1=initial direction increase) Bit 3 Continue (0=same as if Bit0=1 and Bit1=Bit2)

The possible combinations and resulting shapes are:

Binary Hex Shape 00XX 00h-03h \_________ (same as 09h) 01XX 04h-07h /_________ (same as 0Fh) 1000 08h \\\\\\\\\\ 1001 09h \_________ (volume remains quiet) 1010 0Ah \/\/\/\/\/ 1011 0Bh \""""""""" (volume remains high) 1100 0Ch ////////// 1101 0Dh /""""""""" (volume remains high) 1110 0Eh /\/\/\/\/\ 1111 0Fh /_________ (volume remains quiet)

We can observe that there are only 8 resulting shapes even though they are selected by using a 4-bit value.

When using the volume envelope generator, the volume is always increased from 00h to 0Fh (or vice versa), it is not possible to specify a starting/ending point (like from 00h to 07h).

Writing to this register (re-)starts the envelope.

0Eh - External Dataregister Port A

This register receives data from the CPC keyboard (or joystick), for more information read the chapter about the CPC Keyboard Matrix.

This register can be also used as output port by setting bit 6 of the PSG control register to 1 (that would allow to use the six data pins of the joystick connector to output data to external hardware).

0Fh - External Dataregister Port B

This register is not used in CPC computers. In detail, a AY-3-8910 sound chip would have external connectors for this register, so that it could be used as a further IO port, but the CPC's sound chip (AY-3-8912, in 28 pin package) doesn't have such connectors, even though the register still does exist internally.

The Aleste 520EX (russian CPC clone) is a special case: it has a Yamaha YM2149F chip, with SSG Port B being used as 8bit printer port data.

Noise Generator

The noise generator uses a Linear-Feedback Shift Register algorithm. It is described in detail in the AY-8930 datasheet.

The random number generator of the 8910 is a 17-bit shift register. The input to the shift register is bit0 XOR bit3. Bit0 is the output. This was verified on AY-3-8910 and YM2149 chips.

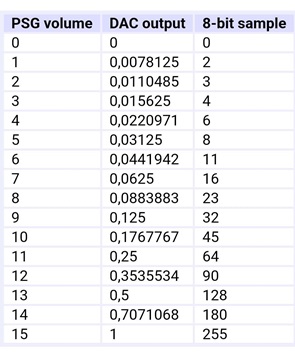

D/A converter table

These are the 16-bit values used in Arkos Tracker. They are more accurate than the datasheet you can find, as they were tested electronically by Grim and Zik directly from a real CPC: 0, 231, 695, 1158, 2084, 2779, 4168, 6716, 8105, 13200, 18294, 24315, 32189, 40757, 52799, 65535

For the record, these are Matthew (Gasman) Westcott measurements (normalised) on its ZX Spectrum: 0, 0.0105, 0.0154, 0.0216, 0.0314, 0.0461, 0.0635, 0.1061, 0.1319, 0.2163, 0.2973, 0.3908, 0.5129, 0.6371, 0.8186, 1

The datasheet show different values: 2 steps down = half values down. Thus, the theoretical formula is f(x) = 2 ^ ((x - 15) / 2) with x between 1 and 15.

This is the volume table used by BSC:

ETO once started testing the output levels (to be fair, with a multimeter only) and it was very close to the theoretical value based on the data sheet and how the CPC mixes the channels. See Discussion on the forum

Volume 0 is indeed silent. It is not just logarithmic attenuation where maximum attenuation of a channel is just very quiet and not silent. Source

Mono and Stereo Output

When using the CPC's external stereo jack, the stereo output causes channel A of the PSG to be heard on the left, channel C to be heard on the right and channel B to be heard in the middle. Source

In that case, channel B is output through a bigger resistor to prevent that this channel appears louder than the others.

Otherwise (when using the built-in speaker), all three channels are mixed at the same intensity. This signal appears to be also sent to the Tape output line also, so a connected Data Recorder could be used to record CPC music also.

BASIC Sound Test

You can test the PSG sound channels by typing simple SOUND commands in BASIC. You should hear a 440Hz sound for 10 seconds at full volume for each of these commands:

SOUND 1,440,1000,15 should produce sound in the left speaker. (channel A) SOUND 2,440,1000,15 should produce sound in both speakers. (channel B) SOUND 4,440,1000,15 should produce sound in the right speaker. (channel C)

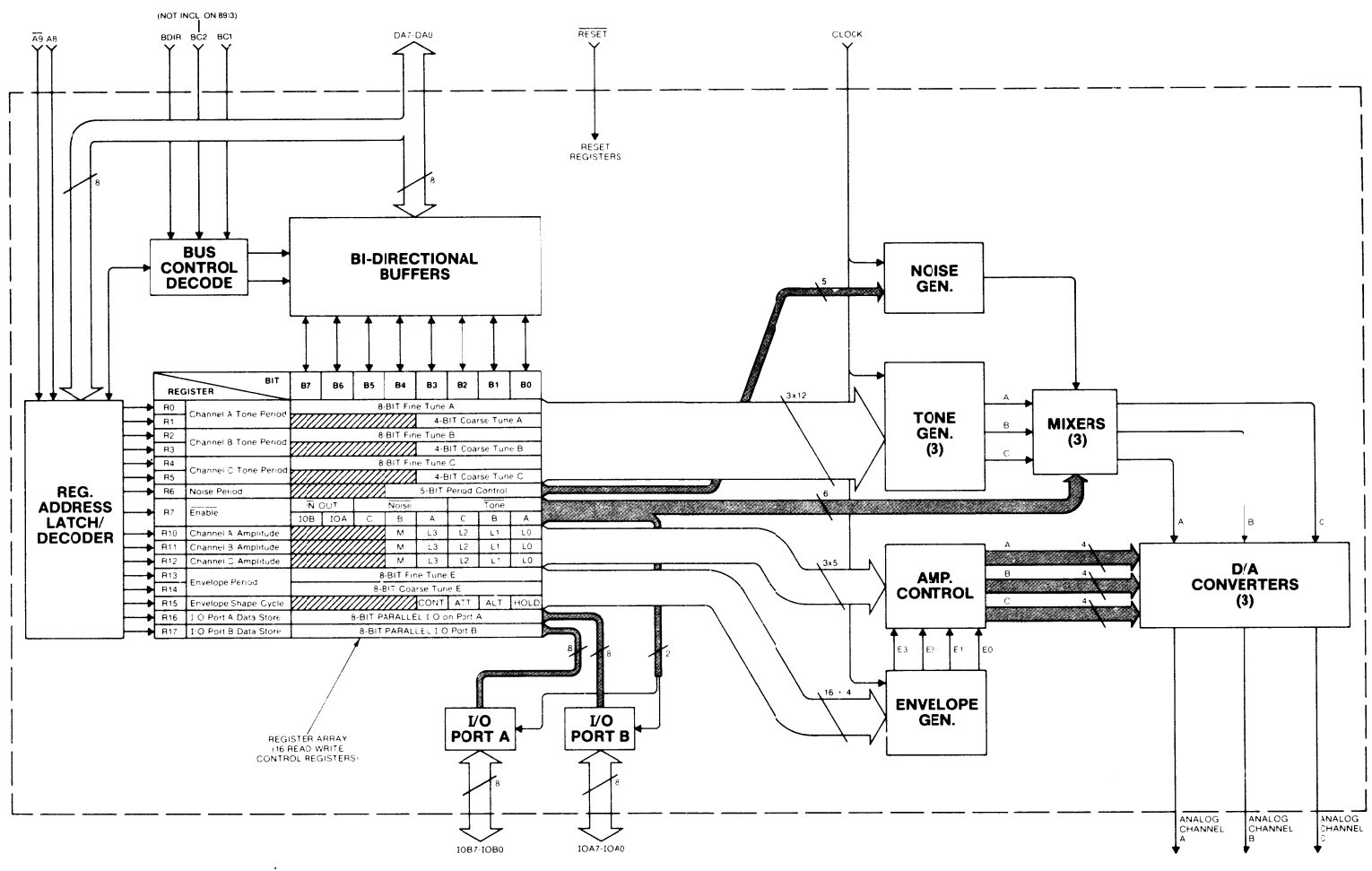

Block Diagram

Much like the CRTC chip, the PSG consists of a few simple functional blocks consisting of counters, equality comparators and some fairly simple logic.

Careful studies of the chip output prove that the chip counts up from 0 until the counter becomes greater or equal to the period, at which point the output flips and the counter resets to 0. (This means that shortening the period can cause an immediate flip if the phase counter is already past the new period value.)

This is an important difference when the program is rapidly changing the period to modulate the sound. This is worthwhile noting, since the datasheets say that the chip counts down.

Also, note that period = 0 is the same as period = 1. This is mentioned in the YM2203 datasheet. However, this does NOT apply to the Envelope period. In that case, period = 0 is half as period = 1. Source (Does this last sentence apply only to the SSG or to the PSG as well?)

The tones, the noise, and envelope are never halted. All of them are continually active whether or not they're connected to an audible output.

Things that have been verified not to halt things: Source

- Volume 0 does not halt tone or noise

- Tone disable bit does not halt tone

- Setting all 3 noise disable bits does not halt noise

- Clearing all 3 channel volume envelope bits does not halt envelope

- Period value of 0 does not halt any of these (treated as period 1 in all cases)

Schematics

The PSG is driven by an external clock at 1MHz provided by the Gate Array. The AY chip has an internal clock divider by 8 which means that it works internally at 125KHz, outputting 125,000 samples per second for each channel.

The BC2 and A8 pins are always equal to 1 as they are connected to +5V. The /A9 pin is non-existent on the AY-3-8912 model.

On the Amstrad CPC 6128 chassis diagram, we can see how the 3 channels of the PSG are mixed to the stereo jack (with channel B being split in half between the left and right output). And the 3 channels being mixed in equal parts to mono for the speaker and tape port. Source

Chip Variants

The PSG chip family is composed of 3 variants: the AY-3-8910 with two 8-bit I/O ports, the AY-3-8912 with one 8-bit I/O port and the AY-3-8913 with no I/O port. In addition to the CPC, these chips were also used in the KC Compact, ZX Spectrum, MSX, Oric, Vectrex, Intellivision and in the Mockingboard expansion for the Apple II.

Yamaha produced the SSG (Software-controlled Sound Generator) chip family (YM2149F, YM3439, YMZ294, YMZ284, YMZ285) which is a quasi-clone of the PSG. The main difference is that the envelope counter on the PSG has 16 steps. On the SSG it has twice the steps, happening twice as fast. This chip equips the Atari ST, Aleste 520EX and some MSX computers. It is also used in the PlayCity expansion.

The SSG has also been integrated as a component inside some of the arcade soundchips of the Yamaha OPN family. That's why you can find it in the Neo-Geo as a component inside the YM2610 soundchip. And the same is true for the OPN3 soundchip of the Play2CPC expansion.

The chip is clocked differently depending on the computer: ZX Spectrum: 1773400 Hz ; Pentagon: 1750000 Hz ; MSX: 1789772 Hz ; CPC: 1000000 Hz ; Atari ST: 2000000 Hz. Toshiba T7766A, Winbond WF19054, JFC 95101 and File KC89C72 are clones of the PSG. Source

The PSG chip competed with the DCSG (Digital Complex Sound Generator) chip family (SN76489, SN94624, TMS9919) by Texas Instruments. The DCSG has similar sounding features except that it does not have any envelope control and that its noise generator has its own dedicated channel.

The EPSG (AY-3-8930), used in the Covox Sound Master soundcard on PCs, is a register-compatible evolution of the AY-3-8910:

- The pulse width can be changed from square to 8 other duty cycles

- There are 3 independent envelope generators, 1 for each channel

- The amplitude control is more accurate (5-bit instead of 4-bit)

- The tone period setting is more accurate (16-bit instead of 12-bit)

- The noise period setting is more accurate (8-bit instead of 5-bit)

- The noise tone can be changed by applying an AND and OR mask to the output