The final cost down models came just before the release of the Amstrad plus. The same chip was used within the CPC464 and CPC6128.

In CRTC terms it operates almost the same as the CRTC within the Plus ASIC.

Costdown IC pinout information

The following information relating to the pins of the IC was tested and verified by Gerald:

L4N6 pin

While it is connected to GND on the 6128, it is left unconnected on the 464 and seems to be internally pulled up.

In 464 mode :

- the /ROM2 signal is always high : ROM7 selection is not handled on board.

- the /CAS1 signal is always high : RAM extension is not handled on board.

In 6128 mode :

- the /ROM2 signal is handled on board.

- the /CAS1 is handled on board, with the expected result of getting garbage instead of base RAM when using RAM selection other than C0

- CPC does get stuck after displaying the copyright message and before the "BASIC 1.0" message.

Extension RAM management

In 464 mode :

- The RAMDIS signal IS taken into account. That mean that extension that does not force the MREQn will work. This include the SymbifaceII

- The C3 mode is NOT supported, as on regular 464.

In 6128 mode :

- Garbage all the way on extension RAM with no extension connected, as expected as no ram is there ;D

- With an extension, C3 is working as expected

- adding 41464 in the alternate footprint and connected to CAS1 instead of CAS0 may transform the 464 in 4128 ;)

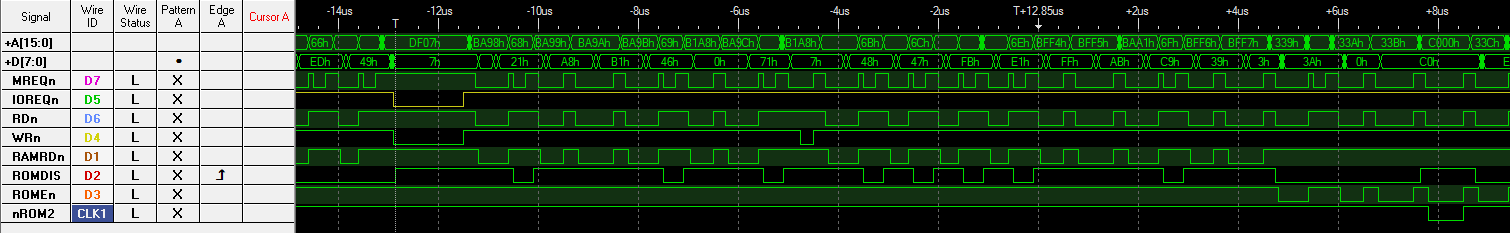

ROM7 and ROMDIS in 6128 mode

- Well, no luck. ROMDIS does not prevent internal ROM7 to be selected

- ROMDIS act as an output when ROM7 is selected (However I need to re-check that it is only happening on ROM 7)

- ROMDIS act as the DDI ROMDIS as it is active even during ram access 10943-0

/EXP

When the DDI1 extension is not plugged, /EXP is pulled high, and /ROM2 signal is in fact ROM0 and replace the BASIC. As no ROM is connected, it just crash !

Bonus

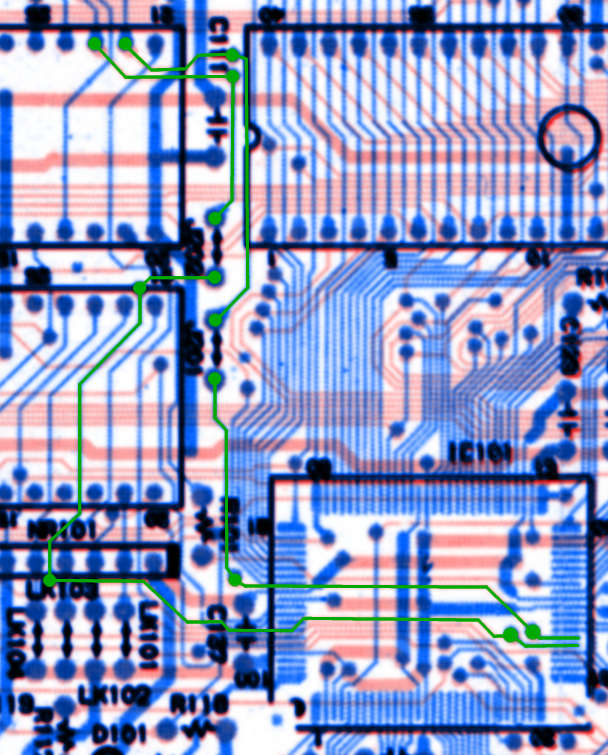

- on the following page, Gate Array and ASIC Pin-Outs - CPCWiki, pin 35 and 36 are undocumented.

- on the PCB in the amendment service manual, these to pins goes to the FDC thru links : pin 35 to DATA, pin 36 to WINDOW 10945-1

- Looks like amstrad was designing its own data separator and planned to use it on this version of the CPC. But As hinted in Arnold V specs - CPCWiki, it was not ready.