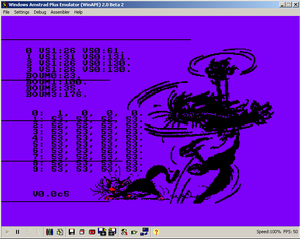

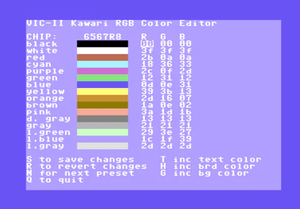

(→VIDEO: C64 option) |

|||

| Line 1: | Line 1: | ||

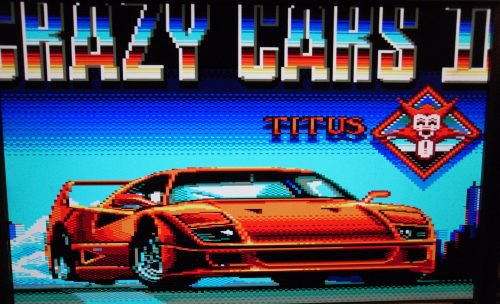

| + | [[File:FPGAmstrad_cc2.jpg]] | ||

| + | |||

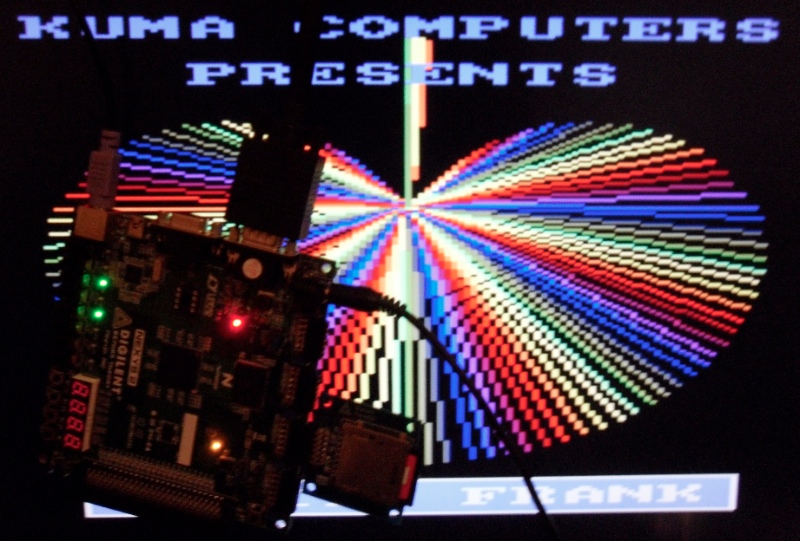

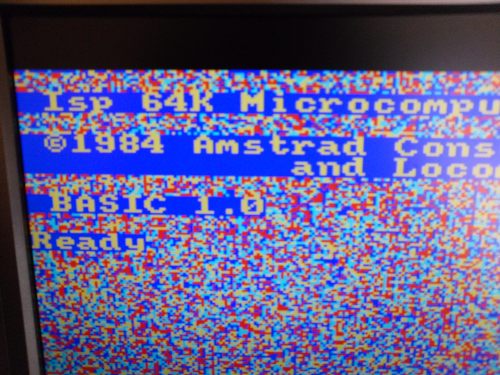

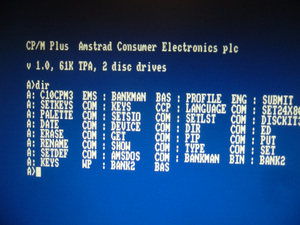

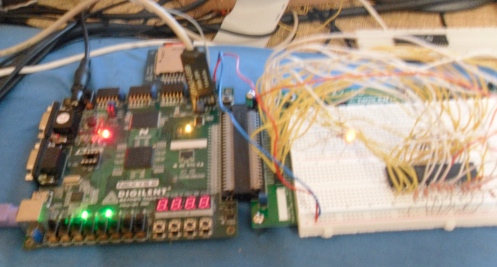

This is a VHDL version of Amstrad CPC 6128 running on FPGA starter-kit NEXYS2 500k-gates from Digilent. | This is a VHDL version of Amstrad CPC 6128 running on FPGA starter-kit NEXYS2 500k-gates from Digilent. | ||

| − | A starter-kit is a | + | A starter-kit is a board made for learning FPGA, so it is a standard FPGA development board. |

| + | Please refer to [[http://github.com/mist-devel/mist-board/wiki/CoreDocAmstrad MiST-board CoreDocAmstrad]] for the final user version, running on MiST-board platform. | ||

| + | |||

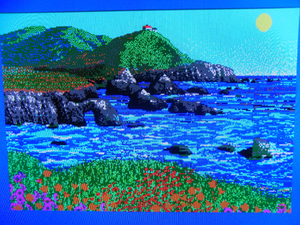

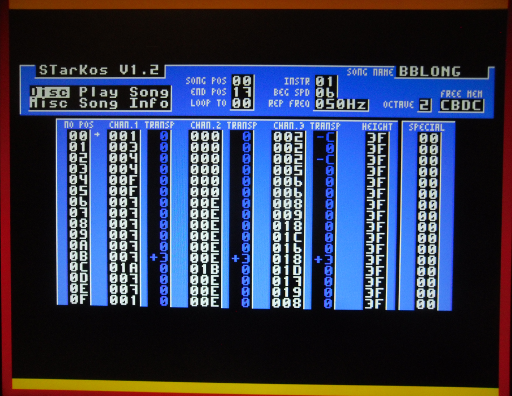

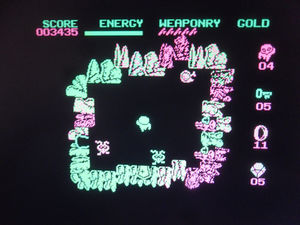

| + | Some games running on it : 1942 1943, 3D grand prix, A view to a kill, Action Fighter, animated strip poker, Antiriad, Arachnaphobia, Arkanoid, Arkanoid Revenge of Doh, Asphalt, Axiens, Barbarian MH, Barbarian PA, Barbarian II, Battleships, Bomb Jack I and II, Boulder Dash, Bruce Lee, Bubble Ghost, Buggy Boy, Bully's Sporting Darts, Cauldron I and II, Chase HQ, Chicken Chase, Classic Axiens, Classic Invaders, Crazy Cars, Crazy Snake, Dan Dare I II and III, Dizzy 7, Donkey Kong, Double Dragon I and II, Druid, E-Motion, Exolon, Express, Fruity Frank, Ghost'n'Goblins, Golden Axe, Gryzor, Heart Land, Hold-up, Hyper bowl, Ikari Warriors, Impossible Mission, Invasion of the Zombie Monsters, Iron Lord, Killapede, Klax64, Laser Squad, Light Force, Locomotion, Lode Runner, Macadam Bumper, Mange-Cailloux, Mario Bros, Maze Mania, P47, POP-UP, Prince of Persia, Prohibition, Realm, Rebel Star, Rick Dangerous I and II, R-Typeee, Rock Raid, Rogue, Rygar, Salamander, Sapiens, Shinobi, Sim City, Sorcery, Spectra, Spherica, Spin Dizzy, Star Ranger, Star Quake, Star Wars, Strider II, Super Ski, Superkid In Space, Tank Command, Tempest, Tetris 95, The Duct, The Empire Strikes Back, Trail Blazer, Trakers, Turbo Tortoise, Turrican I and II, Venoms, Victory Road, Vixen, WEC Le Mans, West Bank, Wizard's Lair, Word Cup Challenge, Word Series Baseball, Xevious, Xor, Zolyx. | ||

---- | ---- | ||

| + | [[File:ghostngoblins.jpg]] | ||

| + | |||

== How to assemble it == | == How to assemble it == | ||

| − | + | NEXYS2 Xilinx version is obsolete, it is still describe here for history reason (showing the prototyping part). Please refer to [[http://github.com/mist-devel/mist-board/wiki/CoreDocAmstrad MiST-board CoreDocAmstrad]] for the final user version, running on MiST-board platform. | |

| − | + | '''You need:''' | |

| − | - a "PMODSD" module for reading sdcard | + | *a "NEXYS2 500kgates" starter kit from Diligent [[http://www.digilentinc.com/Products/Detail.cfm?Prod=NEXYS2]] (1200kgates should be better for future version => in fact I choosen NEXYS4, it is same RAM inside) also in France : [[http://www.lextronic.fr/]] or in Germany : [[http://www.trenz-electronic.de/]] |

| + | *a "PMODSD" module for reading sdcard [[http://www.digilentinc.com/Products/Detail.cfm?NavPath=2,401,513&Prod=PMOD-SD]] | ||

| + | *an alimentation (cause they don't give it with starter kit) [[http://www.digilentinc.com/Products/Catalog.cfm?NavPath=2,393&Cat=3#DTSWPS]] | ||

| + | *optionally a DIGILENT USB JTAG (normally starter kit can be programmed directly by usb, but I don't have tested this way) [[http://www.digilentinc.com/Products/Detail.cfm?Prod=JTAG-USB]] | ||

| + | *a 4GB SDCARD (no more), I have exactly a "SDHC 4GB class4 Verbatim" | ||

| + | *the binary of this project (candidate 002) : source+500k-gates binary [[http://yunyunaof.free.fr/BuildYourOwnZ80Computer_amstrad_vhdl_002_repack.zip]] ; 1200k-gates binary [[http://yunyunAoF.free.fr/amstrad_switch_z80_vga_sd_orion_candidate_002_1200k_binary.zip]] | ||

| + | *several ROM files: OS6128.ROM BASIC1-1.ROM AMSDOS.ROM (from JavaCPC[[http://sourceforge.net/projects/javacpc/]]); MAXAM.ROM[[http://www.cpcwiki.eu/index.php/MAXAM#Download]] | ||

| + | *one or more DSK files : TEMPEST.DSK[[http://www.cpcgamereviews.com/t/index2.html#tempest]] ARKANOID.DSK[[http://www.cpcgamereviews.com/a/index7.html#arkanoid]] FRUITY.DSK[[http://www.cpcgamereviews.com/f/index7.html#fruity_frank]] BRUCELEE.DSK[[http://www.cpcgamereviews.com/b/index12.html#bruce_lee]] CHASEHQ.DSK[[http://www.cpcgamereviews.com/c/index4.html#chase_hq]] WIZLAIR.DSK[[http://www.cpcgamereviews.com/w/index4.html#wizards_lair]] XEVIOUS.DSK[[http://www.cpcgamereviews.com/x/index.html#xevious]] BOULDER.DSK[[http://www.cpcgamereviews.com/b/index10.html#boulder_dash]] CLASSIC_AXIENS.DSK[[http://www.cpcgamereviews.com/c/index6.html#classic_axiens]] CLASSIC_INVADERS.DSK[[http://www.cpcgamereviews.com/c/index6.html#classic_invaders]] GRYZOR.DSK[[http://www.romnation.net/srv/roms/3452/amstrad/Gryzor-UK-1987.html]] PRINCE.DSK[[http://www.cpcgamereviews.com/p/index7.html#prince_of_persia]] BUGGY.DSK[[http://www.cpcgamereviews.com/b/index13.html#buggy_boy]] TRAIL.DSK[[http://www.cpcgamereviews.com/t/index9.html#trailblazer]] P47.DSK[[http://www.cpcgamereviews.com/p/index3.html#p-47_the_freedom_fighter]] SUPER_SKI.DSK[[http://www.cpcgamereviews.com/s/index24.html#super_ski]] ACTION_FIGHTER.DSK[[http://www.cpcgamereviews.com/a/index.html#action_fighter]] | ||

| − | - | + | A package that contains minimum set of ROM and DSK for filling simply sdcard [[http://yunyunAoF.free.fr/OS6128_BASIC1-1_AMSDOS_MAXAM.zip]] (OS6128, BASIC1-1, AMSDOS, MAXAM) |

| − | + | <br> '''You have to:''' | |

| − | + | *program FPGA with the binary file "amstrad_switch_z80_vga_sd.bit" of this project, for it I use Digilent Adept software and my USB JTAG cable | |

| + | *format your 4GB SDCARD in FAT32 4096 byte allocation size | ||

| + | *copy ROM and DSK on SDCARD | ||

| + | *plug PMODSD on slot JC1 of starter kit, and set all 8 switches to 0 | ||

| + | *plug VGA, and turn on starter kit | ||

| − | + | [[File:FPGAmstrad_minimal_plug.jpg]] | |

| − | + | '''You can:''' | |

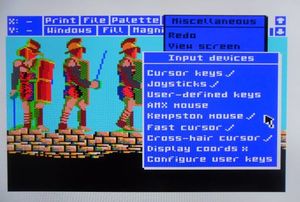

| − | + | *plug a PS/2 keyboard, and type "cat" | |

| + | *increment switch to select another disk at boot, if screen became RED, it's that binary value done by switches is too big, leds are doing a small animation when a disk is correctly loaded | ||

| + | *plug principal joystick on slot JB1 (Vcc 3.3v is common) | ||

| + | *plug another joystick on slot JA1 (Vcc 3.3v is common) | ||

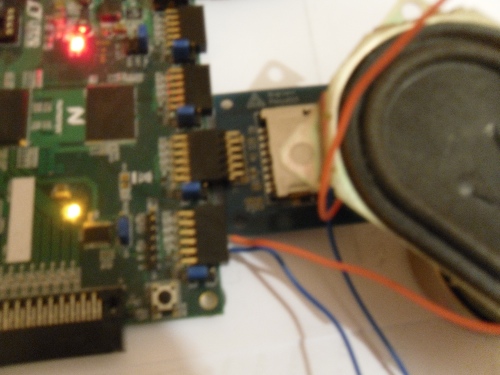

| + | *plug a jack on slot JD1, one at upper GND plug, and second wire at next plug, just at left of it (if it was 3.3v Vcc, choose the right one instead) | ||

| − | + | [[File:FPGAmstrad_sound_plug.jpg]] | |

| − | + | Wires are plugs at upper part of pmod D. | |

| − | + | From bottom to upper: [nothing: Vcc 3.3v] [blue: GND] [red: sound] | |

| + | Sure you can connect a jack... | ||

| − | ' | + | And two joysticks. |

| + | On pmod B: bottom is (both) 3.3v, so joystick's common, next is (both) GND (not used), and others are joystick connections, to test manually :) | ||

| − | + | [[File:FPGAmstrad.jpg]] | |

| − | - | + | ---- |

| − | - | + | ==Video== |

| + | http://www.youtube.com/watch?v=Z8FB_eIy8LY | ||

| + | ---- | ||

| − | + | == Last news about this project == | |

| + | In August 2025, I refactor the OSD menu, adding also an 3rd palette : orange. | ||

| − | + | In MaY 2020, I add Sorgelig formula for WAIT_n=quick, no more table of instruction time in code, just a simple WAIT_n formula. | |

| − | + | In MaY 2019, I add cassette feature. | |

| − | - | + | In August 2018, totally desperated -around time and level of efforts- about reaching next step focus around Z80 range, here came Sorgelig, he is working around port of FPGAmstrad into the MiSTer FPGA platform, and make during his step an intermediate jump step on MiST-board called "Amstrad_MiST" full of verilog as he seems to love. And, as a specialist of Z80 core, I just send him Z80 testbenches I collected since, he then corrected the Z80 fully this way, I merged, resulting this next current checkpoint. |

| − | + | In May 2018, I programmed my first CPC game http://www.pouet.net/prod.php?which=75855 following JDVA youtube tutorial since january, they are based on CPCMania 2005's website knowledge about programing in CPC using SDCC. I think that if I do progress this way enough, I'll implement my own CPC testbenches, needed for reaching next realise of FPGAmstrad (I did it : Moustache testbench) | |

| − | - | + | [[File:Mk2-cpc-600x350.png|thumbnail|Image converted to CPC by SuTeKH/Epyteo]] |

| − | + | In January 2018, Jepalza has ported FPGAmstrad from this wiki (Xilinx version, principe of concept 2011) on spanish ZX-Uno low-cost FPGA final platform (three times cheaper than MiST-board/same Xilinx chip poc 2011/chip used at 100%). So I bought a ZX-Uno to help around this fork, merging components. Normaly I can go a little further later (CRTC0, joystick), and then go back to MiST-board :) | |

| − | + | https://www.youtube.com/watch?v=tpr9xxx1rsA | |

| − | + | ||

| − | + | In May 2017, FPGAmstrad TV mode is validated using a TV from Tetalab group. | |

| − | + | ||

| − | + | In February 2017, CRTC1 is also implemented following JavaCPC's source code, now you can choose between CRTC0 and CRTC1 in the OSD menu. | |

| − | + | In January 2017, scanlines mode is implemented, you can select it from the OSD menu. | |

| − | + | In December 2017, implementing green screen, using "Les Sucres en Morceaux" tutorial. | |

| − | + | In September 2016, FPGAmstrad does use external RAM as RAM+VRAM, no more "LowerVRAM/UpperVRAM" switches to select in the OSD menu. | |

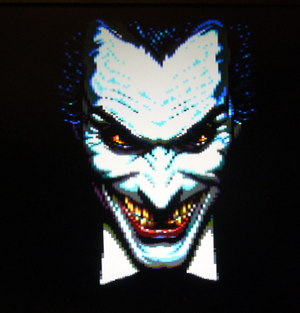

| − | + | [[File:Fpgamstrad jocker batdemo.png|thumbnail|Using 64K of VRAM...]] | |

| − | ' | + | In August 2016, FPGAmstrad does pass some arnoldemu's testbench : PPI PSG CPCTEST. |

| − | + | In February 2016, FPGAmstrad has a TV mode (original signal) | |

| − | + | In September 2016, FPGAmstrad has write access on both disk drives, and can change dsk. | |

| − | - | + | In March 2015, FPGAmstrad is stable on MiST-board, please refer to [http://github.com/mist-devel/mist-board/wiki/CoreDocAmstrad MiST-board CoreDocAmstrad] and [http://code.google.com/p/mist-board/source/browse/#svn/trunk/bin/cores/amstrad mist-board amstrad bin core] |

| − | + | In December 2014, FPGAmstrad is stable on NEXYS4, WIP, BOOTLOADER improved, VRAM improved (with BORDER colors !), RAM relaxed, no more timeout in keyboard key-press, Ghouls 'n' Ghosts, Macadam, a lot more to do. 14% of platform is used. | |

| + | In November 2014, I bought MiST-board, with two USB pro joysticks. | ||

| + | |||

| + | In September 2014, I bought NEXYS4, more powerfull than NEXYS2, with same external RAM, internal mini-sd, no PS/2 (it is a pmod option)... I have some patchs to make (MSB FAT32 offset). I would like to make a USB sniffer also with it (usb to ethernet (wireshark)) | ||

---- | ---- | ||

| − | == Effort done == | + | |

| − | Instruction timing | + | == Contact == |

| + | |||

| + | I am Freemac, my IRL name is Renaud Hélias. | ||

| + | |||

| + | You can contact me by mail to renaudhelias @t gmail d0t com, if you have questions about assembling this project or running it in MiST-board final platform. | ||

| + | |||

| + | Follow me on [http://plus.google.com/u/0/102709294612470681079 my google plus account]! | ||

| + | |||

| + | ---- | ||

| + | |||

| + | == Tests done == | ||

| + | |||

| + | Great games that are running properly are listed at top of page. | ||

| + | |||

| + | ===On MiST-board CoreAmstrad version=== | ||

| + | Games that doesn't run are : | ||

| + | *'''007 The Living Daylight.dsk''': problem with VSYNC. Certainly two VSYNC per frame, GA ignoring the second one. | ||

| + | *'''ACPC_logon_system.dsk''': text scrolling lag. This demo will be used for horizontal ink calibration (when I’ll buy a luxurious FPGA platform... I need in fact 224KB of internal RAM to do it), and CRTC overcounts. | ||

| + | *'''split ink demo.dsk''': (from cpcrulez) : may help about ink raster calibration. | ||

| + | *'''Sultan's Maze.dsk''': does need the right part of keyboard (F0-F9 are used for directions in this game) | ||

| + | *'''Orion Primes.dsk''': does display "secteurs entrelacés" - "vérifiez votre copie", a FDC problem, perhaps "sectorId++" is not the good way to reach next sector, or else two tracks in one track. Does pass on Sorgelig fork. | ||

| + | *'''Batman_Forever.dsk''': some problem during flying chip demo part (one garbage line), and several rupture showing ghost lines around Vcc=0. Rupture solved in r005.8.16c4, but flying chip now show a half garbage of pixels. Batman seems CRTC1. Problems with FDC in r005.8.16 (does slow animations, like if I missed some "not ready" signal ?) | ||

| + | *'''30YMD.dsk''': in Benediction demo, at bottom some time you see some ghosts of central animation (too many HSync per screen ?), solved in r005.8.16 (CRTC0 seems perfectly implemented). 30YMD seems CRTC0, running fine except that changing disk feature does still fail (inserted/not inserted/inserted signal ?) | ||

| + | *'''imperial_mahjong.dsk''': modern EXA/EXA2 resolution not passing my color pallet heuristic :p - does pass on Sorgelig fork. | ||

| + | *'''rtypeee.dsk''': at begin of presentation, a draw of "jack plug" is done in a strange video mode, more than 200 pixels of height !, see [http://cpc.sylvestre.org/musee/musee_flipping_lace.html flipping lace] | ||

| + | *'''S&Koh.dsk''': LOGON SYSTEM, black screen in r005.8.4... damn | ||

| + | *'''Fres Fighter II Turbo.dsk''': FDC problem, cannot be launched. | ||

| + | *'''Seascape.dsk''': Devilmarkus, using scandb50Hz and MEM_wr=slow, does display, but a flower petal at bottom is drawn in blue. A good raster test. Test on real 6128 [http://www.cpcwiki.eu/forum/demos/seascape-cpc-by-impact-on-original-cpc-6128/ forum: Seascape CPC by Impact - on original CPC 6128 ?] - by Emashzed : type 1 is perfect (no blue on bottom right flowers, no blue on middle triangle rock), type 2 has bright cyan squares (one on bottom right flowers, and one on middle triangle rock. Calibrated OK in r005.8.16.5 using OSD VGA:scandb50Hz. Does pass on Sorgelig fork. | ||

| + | [[File:Seaspace-type1_MiST-board_CoreAmstrad-r005.8.16.5|thumbnail|Seascape (type 1) - r005.8.16.5]] | ||

| + | *'''Megablasters[original].dsk''': has a 2 pixels glich border on left side. Certainly final HSYNC offset problem, as on Super Cauldron normaly the right (not left) border has to be selected to get a nice bottom bar in game (actually too centered) | ||

| + | *'''Edge_Grinder.dsk''': screen not stable horizontally, music change speed during game ? Does pass on Sorgelig fork. | ||

| + | *'''Welcome To Amstrad CPC 6128.dsk''': does display "Incompatible BASIC installed" message. | ||

| + | *'''phX.dsk''': does begin to pass on r005.8.16. Does pass completly on Sorgelig fork (scandoubler). Does finish on amstrad_180804_r005.8.16.5. Does show vertical bars with CRTC0, no display during end scroll part. Does freeze at middle on amstrad_180804_r005.8.16.6 (doesn't launch the read of disk), does pass on Sorgelig fork but song is 2 times slown down before reaching this part. Did pass one time on amstrad_200527_r005.8.16.8.5c1.rbf (CRTC0 WAIT_n:quick (Sorgelig GA simple formula)), but I was lucky. Did pass one time on amstrad_200527_r005.8.16.8.5c2.rbf (CRTC1 WAIT_n:quick) except vertical bars of begin. Seems that launching Pinball Dreams CRTC1 (until menu of boards) before (soft reset (page up key) and) PhX CRTC0 does unlock PhX. | ||

| + | *'''Ghouls'n'Ghost.dsk''': does fail on r005.8.16.2 : time going to zero in 3 seconds, is fine in r005.8.15.2, fine also on Sorgelig fork... also unlocked by Sorgelig in r005.8.16.3 ! | ||

| + | * '''Ultimate Megademo (Face Hugger).dsk''': First part is better using CRTC0. Ending part (one just after Lemmings part), a double VSYNC problem (a small scrolling text instead of... a lot of things), music OK during this ending. | ||

| + | |||

| + | '''Arkanoid.dsk''' stars use rupture address (changing address several time during display of one image), it is now supported on "candidate 001" version of FPGAmstrad. Run better in r005.9.11e than in r005.9.11. | ||

| + | |||

| + | '''Gryzor''' and '''Prince of Percia''' use rupture ink/mode (changing ink and mode during display of one image), it is now supported on "candidate 002" version of FPGAmstrad | ||

| + | |||

| + | Gryzor is really sensitive to Amstrad general stability : do press esc at start menu does activate music during game, if no music, FPGAmstrad is in an instable version (last known stable version r003.8) | ||

| + | |||

| + | '''Crazycars2.dsk''' first car image use 32KB of VRAM, it is now supported on "candidate 001" version of FPGAmstrad. | ||

| + | |||

| + | '''Ghouls'n'Ghost.dsk''' / '''Ecole.dsk''' does need RAM write when writing in ROM (RAM is beside ROM, hard to emulate with asynchronous SDRAM controler, MiST does use a hacked synchronous RAM done for that) | ||

| + | |||

| + | '''moktar.dsk''' / '''super_cauldron.dsk''' does run fine since r004.8.1.1. Morkar run fine in r005.8.16c4 using CRTC0 and MEM_wr=slow. Super Cauldron bottom bar is fine in r005.8.16.4 when we select "right border" (instead of default left one) during "screen synchro" menu welcome. | ||

| + | |||

| + | '''CPC Aventure''' does run fine since r005.2 (message about turning disk now displayed) | ||

| + | |||

| + | '''prehistorik.dsk''' does run fine since r005.2 (key can now be pressed in intro demo) | ||

| + | |||

| + | '''Sim City''' and '''Hero Quest''' run fine since r005.2 (it was about "key always pressed"), but does need a hard boot (not quick reset keyboard key), certainly a small problem of component init state. '''Sim City''' hack demo intro does run better using A-Z80 instead of T80 (2/3 of luck). | ||

| + | |||

| + | A lot of demos don't pass in NEXYS4 FPGAmstrad's version (I need to implement back the SDRAM hacked in MiST board FPGAmstrad version). [http://cpcrulez.fr/Scene_Demos/index.php CPCRULES demos] is a cool ressource as it contains simple dsk formats. | ||

| + | |||

| + | '''crazycar.dsk''' does use lowerVRAM=00 (&0000-3FFF and &C000-FFFF area for VRAM) | ||

| + | |||

| + | '''crazycar2.dsk''' does use lowerVRAM=10 (&8000-BFFF and &C000-FFFF area for VRAM) while overscan presentation, and lowerVRAM=00 (&0000-3FFF and &C000-FFFF area for VRAM) during play. Run fine since r005.7 | ||

| + | |||

| + | '''buggyboy.dsk''': I found one dsk running correctly and another not : problem on this last one is about turning left/right effect : the car continues straight (it seems a prototype bad version) | ||

| + | |||

| + | '''superski.dsk''' : don't forget to disable autofire, in jump, do press fire+up or down. | ||

| + | |||

| + | '''protext.rom''': All right since r004 (before, in edit mode, if I pressed continuously one key, it did write ten letter and freeze/crash. Do note that a number is incremented in live at top right, so this is a complex software, good for keyboard vector stability tests) | ||

| + | |||

| + | '''atomdriv.dsk''': unlocked since r004.5 (the game and music did freeze (ROM unplugged shall return xFF)) | ||

| + | |||

| + | '''rtypeee.dsk''': unlocked since r004.7. Does use special read FDC cmd, with BOT different of EOT (begin of track/end of track), so reading several 512 bytes blocks in one FDC command only. | ||

| + | |||

| + | '''Arkanoid Revenge of Doh''' and '''Asphalt''' are two games that doesn't support ROM extensions : Doh starts to show small bad layers, and Asphalt does crash and reset before main menu... if you add another gadget ROM. | ||

| + | |||

| + | '''antiriad.dsk''': no keyboard/joystick between r004.5 and r004.7. By adding pull-up at r004.5 I lost this game, by implementing a better PPI in r004.8 this game run fine : Antiriad is back ! | ||

| + | |||

| + | '''-circles.dsk''': this demo freeze does since r004.8 (PPI border effect ?) and is back since r005.5, it was nice to calibrate SOUND clock : I did generate 8 candidates of synchronizing this clock (1MHz from 4MHz : 1100 0110 0011 1001, and 0.5 deltas : 1100i, 0110i, 0011i, 1001i), only one does not freeze -circles... so I release r005.5 candidate. This demo is a great one around calibrating Yamaha clock. | ||

| + | |||

| + | '''Nigel Mansell's Grand Prix.dsk''': Only one race track seems ok : Monaco (Brazil track does not start). Unclassified : this disk bug also with other emulators, certainly a bad dsk dump here, TOSEC version of Nigel Mansell does run fine (but some legendary traces of "SK bit purpose" needed by here (in FDC, setting SK does jump deleted disk tracks), perhaps to investigate) - update : some tracks unlocked in r005.8.15c61. | ||

| + | |||

| + | '''saboteur2.dsk''': run fine since r005.5 (nice music and then freeze problem), it was about Yamaha clock generator (generated by Gatearray, versus WAIT_n added in short Z80 instruction to let them during all 4 clocks (Z80 in Amstrad does use 4T or 8T instructions (WAIT_n does insert missing T)). Does freeze at welcome since r005.8.7. Back since r005.8.10. | ||

| + | |||

| + | '''tetris95.dsk''' : bad in r005.8.9.2 (4 beep while breaking 3 lines (instead of 3 beep while breaking 3 lines), was correct in r005.8.4. Back since r005.8.10. | ||

| + | |||

| + | '''Battro.dsk''' seems also CRTC1 and does fail completly. Does pass in r005.8.16. | ||

| + | |||

| + | '''arkanoid2.dsk''': don't run in r005.8.13, but fine in r005.8.13e (experimental fork), ok in r005.8.14 (using default OSD value : MEM_WR=quick) | ||

| + | |||

| + | '''trailblazer.dsk''': no more "raster" problem since r005.5, it's now perfect ! Palette heuristic offset (done for unlocking Batman Forever Demo) has a small effect in left (squares are not separated by a black line in first column) - same small defect in TV mode using r005.8.14.2... Thinking about a HSYNC offset of 2 (instead of 1 currently) then also delaying DATA+HDISP of 1 (char) . Has defect on bottom scroll text bar r005.8.16.2, is fine in r005.8.15.2, fine also on Sorgelig fork... also unlocked by Sorgelig in r005.8.16.3 ! | ||

| + | |||

| + | '''commando.dsk''': pixels that should be deleted are not deleted (only VRAM &C000-FFFF seems used), on level 1, the moto is not displayed correctly inside the bridge... but after the bridge :/ - unlocked by Sorgelig in r005.8.16.3 ! | ||

| + | |||

| + | '''Pinball_Dreams__PREVIEW.DSK''': Does run in version r005.8.16.6 using CRTC1 (and WAIT_n=slow). Sorgelig fork does implement interlace (used an welcome screen - eagle) | ||

| + | |||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Game !! Welcome !! Title !! Game | ||

| + | |- | ||

| + | | CrazyCar2 || || 1011 || 0011 | ||

| + | |- | ||

| + | | One || || 0111 || 0011 | ||

| + | |- | ||

| + | | Scarabus || || 0111 || 0011 | ||

| + | |- | ||

| + | | Ace || || || 0010 | ||

| + | |- | ||

| + | | Tintin || 0111 || 1011 || 0111 | ||

| + | |- | ||

| + | | Devil's Crown || || 0001 || 0011 | ||

| + | |- | ||

| + | | Mach 3 || 0111 || 0111 || 0110 | ||

| + | |- | ||

| + | | Paranoia (1994) || || 1011 || 0001 | ||

| + | |- | ||

| + | | World Class Rugby || 1011 || 0001 || 0001 | ||

| + | |- | ||

| + | | Miam Cobra || || || 1001 | ||

| + | |- | ||

| + | | Galivan || || || 0001 | ||

| + | |} | ||

| + | |||

| + | '''XOR.dsk''' does use lowerVRAM=01 (&4000-7FFF and &C000-FFFF area for VRAM) | ||

| + | |||

| + | TODO : | ||

| + | |||

| + | *To test also : [http://www.speccy.pl/archive/prod.php?id=335 Unlimited Bobs (Dr.Piotr).dsk] demo. | ||

| + | |||

| + | ===On MiST-board CoreAmstrad version - TAPES === | ||

| + | |||

| + | https://cpcrulez.fr/GamesTest/legend_of_steel.htm : | ||

| + | Hello, | ||

| + | a nice game, unfortunately graphic error at 50 and 72 Hz. | ||

| + | My monitor can be 50Hz. 48Hz not. | ||

| + | Why does the game show 48Hz on my monitor? | ||

| + | https://cpcrulez.fr/GamesTest/legend_of_steel.htm | ||

| + | Best regards, MiC | ||

| + | |||

| + | List of known running TAPE games (on r005.8.16.8.3c9): A Magician s Apprentice (txt), A Message from Deep Space (txt), A View To A Kill, Aaargh!, '''Academy''' (missile commander 360°), Advanced Destroyer Simulator, Advanced Lawnmoving Simulator (by '''DevilMarkus'''), After Shock (txt+img), '''Aftermath''' (missile commander), Air Attack, Air Traffic Control - Heathrow, Air Traffic Control - Schiphol, '''Airborne Ranger''' (aircraft or walk), Airwolf, Aladdin s Cave, '''Alex Higgins World Snooker''' (pool table), Algebre, Ali Candil Y El Teroso dde Sierra Morena, Alien TurboAmstrad, Alien Syndrome, Aliens The Computer Game, '''Alkahera''' (spacecraft simulator), Alpine games, Alsim, Alternative World Games, Amaurote, Amsgolf, AmstradMagazine Le Survivant, Amstrad Shuffle (card games), Amstrad Tecla a Tecla, Amstroid (txt), '''Amstroids''', Angelique A Grief Encounter (txt), '''Angleball''' (pool table), Animal Vegetable Mineral, Annals of Rome, Antalex (txt), '''All Points Bulletin''' (little car), Apocalipsis New (txt), Arcade Fruit Machine, Arcos, Ariane, Arnhem, '''Asphalt''', Assault Course, Asterix and the Magic Cauldron, Astro Plumber, '''Atahualpa''' (angel), '''Athlete''', Atlantida 3000 (platform), Atlantis Anirog, Atlantis (txt), '''Atomic Battle''' (asteroids), '''Atomic Driver''' (little car), Auftraq In Der Bronx (txt), Aufwarts Zur Rettung (donkey kong), '''Avenger Way of the Tiger II''', Aventure Au Chateau (adventure), '''Azar Menu''', | ||

| + | Abu Simbel Profanation, Ace of Aces, Advanced Pinball Simulator (CPC-Power), After The War, Afteroids (CPC-Power), Agent X 2, Alien Highway, American Football, Amo Del Mundo, Amsgolf, Amsoccer (del key to launch party), Amstrad Unlocked, Animated Strip Poker, Aquad, Arkanoid, Arkanoid II, Arkos, Army Moves, Artura, Ashkeron (txt), Atlantis Anirog, Atom Ant, Auf Wiedersehen Monty, Autocrash, Auxilio Aereo. | ||

| + | |||

| + | Games that doesn't run are : | ||

| + | * '''Action Force.cdt''': freeze during loading, black screen with green border, nothing more. glitch in r005.8.16.8.3c8 | ||

| + | * '''Adidas Championship Football.cdt''': freeze after loading. | ||

| + | * '''Afterburner.cdt''': nothing after load (still black screen with colorfull border) reboot | ||

| + | * '''Alien Attack.cdt''': simple tape, but freeze (idFF : end of tape) saying "is loading". Same using WinAPE. | ||

| + | * '''Alien Legion.cdt''': not enough in line 19 : memory &9FFF. Run in r005.8.16.8.3c9 but no key ? | ||

| + | * '''Alta Tension.cdt''': 007 Living in fact, same vsync problem than disk version. | ||

| + | * '''AMC Astro Marine Corps.cdt''': welcome picture not drawn completely, do load data for nothing and then freeze. | ||

| + | * '''Anatomie.cdt''': end of tape idFF. | ||

| + | * '''Arnold Goes to Somewhere Else.cdt (txt)''': Rewind tape. | ||

| + | * '''Atlantida 3000''': welcome picture seems not fully loaded, but game starting. Same in WinAPE. | ||

| + | * '''ATV Simulator.cdt''': nothing after load (still black screen with colorfull border), reboot | ||

| + | * '''Automec.cdt''': reboot during game (second tape of three) | ||

| + | |||

| + | Back-Tron, Bacterik Dream (puzzle), Bactro (tron), Bactron, Balade Outre-Rhin (txt), '''Ball Breaker II''' (breakout), Ballon Buster (press space to unlock black screen, and another time after welcome screen displayed), Barry McGuigan Word Championship Boxing, Batalla de Inglaterra, Batalla Naval, Battle ships, Battle Tank Simulator, '''Batty''' (breakout), Beat the Clock (scrabble), Behind The Lines (txt), Berks 3, '''Bestial Warrior''' (platform), Beta-2515, '''BeTiled''' (Bejeweled), Better Spelling, Big Trouble in Little China, Blade Runner, Blagger, Blindado, Blitz AmstradAction, Blockbusters, '''Blue Tomb''' (bomberman), BMX Ninja, '''Bob Morane Espacio''', '''Bomb Jack''', Border Harrier (adventure), '''Bosconian 87''' (Asteroids), '''Boulder Dash 3''', Brian Jacks Superstar Challenge (run), Bride of Frankenstein, Bridge (card), Bronx, '''Bubble Bobble 4''', Bubble Dizzy, Buffalo Bill s Rodeo Games, Buggy II, '''Buggy Boy''', Bugs Buster, Bullseye, Bump Set Spike, Bundesliga Manager 3 (tool), Buscate la vida, Business Plus, '''Buster Block''', Ball Crazy, Barbarian, Bataille Pour Midway, Battle for Midway, Beach Buggy Simulator, Bedlam, Beyond the Ice Palace, Bivouac, Black Beard, Blasteroids, Brawn Free (txt), Bruce Lee, Bubble Bobble (2014-06-20), Buitre-Emilio Butragueno Futbol | ||

| + | |||

| + | * '''Back to Reality.cdt''': Rewind tape. | ||

| + | * '''Barbarian II.cdt''': black screen blue border. Welcome screen with glitchs | ||

| + | * '''Beach Head 2.cdt''': freeze load. Reboot id13 | ||

| + | * '''Blood Valley.cdt''': welcome screen, "Read error b" | ||

| + | * '''Bomb Jack 2.cdt''': welcome picture not load completely, freeze. | ||

| + | * '''Boom.cdt''': load until block 16, then freeze. Reboot at block 21. | ||

| + | * '''Booty.cdt''': second welcome screen then freeze. id15 (ear) | ||

| + | * '''Boulder Dash 4.cdt''': not a game but a tool kit, | ||

| + | * '''Brainache.cdt''': no pause at begin of tape, welcome screen turn into black screen at end of tape (idFF) | ||

| + | * '''Bugs.cdt''': "Rewind tape" message | ||

| + | |||

| + | Cap Horn, Cap sur Dakar, Cavebola, Cedric y los Juguetes Perdidos, '''Chessmaster 2000''', Civil War, Cluedo, '''Cobra''' (snake), Coloric, Concurso, Conflit en l an 2000, Crystann Le Donjon de Diamant | ||

| + | |||

| + | * '''CORE Anatomie''': end of tape idFF. | ||

| + | |||

| + | '''Dan Dare 1''', Dances With Bunny Rabbits (txt), Danger Adventurer at work (txt), Danger Mouse In Makin, Dark Side, Dark Star, '''Darts''', De la Terre a la Lune, Deactivators, Deadenders (txt), '''Deadly Evil''' (walk platform), Deathkick (right part of keyboard), '''Deathscape''', Dedalos, '''Defcom1''', Demon Attack, Dempsey and Makepeace, Dernier Metro, Desert Rats, Devil s Castle, Diamond Mine, Diamond Mine 2 (same ?), Die Heilige Rustung Des '''Antiriad''', Die Tiefe (txt), Die You Vicious Fish (txt), '''Digger Barnes''', '''Dimension Omega''', Dirk, Dizzy 2 Treasure Island, Dizzy 4 Magicland, Dizzy 5 Spellbound, Dizzy 6 Prince f the Yolkfolk, Dizzy Down the Rapids, Dominoes (keyboard F1-F7 + space), '''Doodle Bug''' (pacman+), Doomsdark's Revenge (txt), Dr Jackle and Mr Wide, Dracula (txt), Dragon's Lair, Dragons of Flame, Driller, Druids Moon (txt), Duel A Abilene, Dun Darach, Dungeons Amethyst (txt), Dynamite Dan, Dynamix | ||

| + | Daley Thompson Super Test 1, Dark Fusion, Death Stalker, Death Wish 3, Desperado, Die Alien Slime, Dizzy Amstrad Action Special Edition, Dizzy Cristal Kingdom, Double Dragon, Dragon Spirit, Dragontorc, Dustin | ||

| + | |||

| + | * '''Daleks.cdt''': use of right part of keyboard as arrow (not mapped) | ||

| + | * '''Daley Thompson s Olympic Challenge.cdt''': reboot | ||

| + | * '''Damas.cdt''': Rewind Tape | ||

| + | * '''Dark Sceptre.cdt''': Rewind to 04 | ||

| + | * '''Dark Man.cdt''': black screen pink border | ||

| + | * * on r005.8.16.8.1c3 | ||

| + | * '''Death Pit.cdt''': welcome screen not loaded completely idFF | ||

| + | * '''Deliverance.cdt''': black screen pink border, reboot id13 | ||

| + | * '''Demon s Revenge.cdt''': "Searching 00" freeze | ||

| + | * '''Des Chiffres et des Lettres.cdt''': reboot | ||

| + | * '''Dick Tracy''': black screen id15 (ear), idFF (end of tape) | ||

| + | * '''Dizzy 3 Fantasy World''': black screen | ||

| + | * '''Dominator''': black screen pink border | ||

| + | * '''Domino''': Rewind tape | ||

| + | * '''Don't Panic''': no pause, freeze message "SEARCHING", id15 (ear) idFF (end of tape) | ||

| + | * '''Dragon ninja''': welcome screen ok, message "128K MACHINE DETECTED" - "PLEASE WAIT" too long, slower than WinAPE id11 read (datalen=0 does ignore data read ?) | ||

| + | * '''Dynamic Duo''': "Searching 00" freeze | ||

| + | |||

| + | E.X.I.T, Eagle AmstradVideoPlay, '''Eagle''', Edd the duck, Eden Blues, Egg Blitz, El Comecocos, El Cuerpo Humano, El equipo A (A Team), El Formamento, El Foso, El Misterio del Milo, El Prisionero (txt), '''El Secreto de la Tumba''', Electric Fencing, Electro Freddy, Elevator Action, '''Elven Warrior''', Emerald Isle (txt), Emilio Butragueno Futbol, Emlyn Hughes International Soccer, En Busca Del Arca De ma Alianza (txt), Encyclopaedia of War-Ancient Battles, Endurance, Enduro Racer (moto), Enigme a Oxford, '''Enterprise''', '''Equinox''', Escape-Edisoft, Escape from Khoshima (txt), Espacial, Espana-Comunidades Autonomas 1, Espionage, Espionage Island (txt), Euro Boss, Europa Teatro de Operaciones, European 2, European Champions, '''European Soccer Challenge''', Evening Star, Everyone s a Wally, Exolon, Exploring Adventure on the Amstrad (txt), Exterminator, Eye, | ||

| + | E-motion, Echelon, El CID, El juego de la Oca, El Ladron del Sol Purpura, El Poder Oscura, Elektra Glide, Elidon, Emilio Butragueno 2, Emilio Sanchez Vicario Grand Slam, Empire, Enchanted, Endzone, European 5, Every Second Counts, Eye Spy | ||

| + | |||

| + | * '''Eddie Edwards Super Ski''': rewind tape | ||

| + | * '''El Caldero Magic''': return to basic during game, bad charset | ||

| + | * '''El Capitan Trueno''': slow block load, reboot | ||

| + | ** on r005.8.16.8.2c12 | ||

| + | * '''El Gerente''': rewind tape | ||

| + | * '''El Jabato''': blue screen, reboot | ||

| + | * '''El Laberinto del Sultan''': rewind tape | ||

| + | * '''El Tute''': after a certain time doing nothing, "Read error b" | ||

| + | * '''Election''': black screen with blue border, message "LOADING: Please Wait" | ||

| + | * '''Eliminator''': black screen with blue border | ||

| + | * '''Elite''': "Searching 00", id15 (ear), with somes id11 before and after it. | ||

| + | * '''Energy Warrior''': game launched but bad horizontal alignment | ||

| + | * '''Er-bert''': "Press PLAY then any key"; end of tape idFF | ||

| + | * '''Erik the Viking''' (txt): end of tape idFF, no key | ||

| + | * '''Escape from The Planet Of The Robot Monsters''': welcome image OK, then black screen border green | ||

| + | * '''Eswat-Cyber Police''': Cannot insert face B | ||

| + | * '''Execution''': gray screen | ||

| + | * '''Exploding Wall''': black screen red border | ||

| + | * '''Explorer''': reset to BASIC | ||

| + | * '''Express Raider''': yellow screen blue border, message "LOADING: Please Wait" | ||

| + | * '''Extreme''': black screen blue border | ||

| + | |||

| + | Fantasia Diamond (txt), Federation (txt), Feliz Navidad, '''Fernandez Must Die''', Ferry Captain, Fifth Quadrant, '''Feud''' (OK on r005.8.16.8.2c13), Fighter Pilot, Finders Keepers, Fire Ant, Firescape (txt), First Steps With The Mr Men, Flash, Flight Path 737, Flight Simulation, Fluglehrer, Flunky, Fly, Fly Spy, Football manager, Football manager III, '''Forbidden Planet''', Force 4, Forces, Formula 1 Simulator, Formula, Fourth Protocol, Frank Bruno s Boxing, Frank N Stein, Frankenstein (txt), '''Freedom Fighter''', Friss Man, Frontline, '''Frost Byte''', '''Fruity Frank''', Fu-Kung in Las Vegas, '''Fusion 2''' | ||

| + | F-1, Fernando Martin Basket Master, Fiendish Freddy s Big Top O Fun, Firelord, First Past The Post, Five a Side Football, Football Champion, Footballer of the year I, Forgotten Worlds, Formula One, Frankenstein Jnr/Junior, Froggy, Fuego Curzado, Future Knight | ||

| + | |||

| + | * '''F15 Strike Eagle''': black screen blue border, xFF (end of tape) | ||

| + | * '''F16 Combat Pilot''': black screen blue border, xFF (end of tape) | ||

| + | * '''F16 Fighting Falcon''': light gun game | ||

| + | * '''F1 Tornado Simulator''': some vsync problem ? | ||

| + | * '''FA Cup Football''': Rewind tape slow face of tape OK | ||

| + | * '''Fairlight 1 A Prelude''': Rewind tape | ||

| + | * '''Fast Food Dizzy''': black screen, a dot | ||

| + | * * on r005.8.16.8.2c13 | ||

| + | * '''Fighter Bomber''': black screen pink border, reboot | ||

| + | * '''Fighting Soccer''': black screen blue border, reboot | ||

| + | * '''Fire and Forget 1''': Rewind tape, idFF (end of tape) | ||

| + | * '''Firezone''': use right part of keyboard | ||

| + | * '''Flash Gordon''': Read error b | ||

| + | * '''Flying Shark''': Searching 00, strange id60 (end of tape). Rewind to 12 | ||

| + | * '''Football Director''': welcome picture not load completely, freeze, xFF (end of tape) | ||

| + | * '''Football Frenzy''': Rewind tape | ||

| + | * '''Football manager II''': welcome image and music, then Rewind tape | ||

| + | * '''Football Manager World Cup Edition''': welcome screen, no more idFF (end of tape) | ||

| + | * '''Footballer of the year II''': glitch | ||

| + | * '''Freddy Hardest 1''': black screen blue border | ||

| + | * '''Freddy Hardest 2''': reboot | ||

| + | * '''Freestyle BMX Simulator''': black screen | ||

| + | * '''Friday The 13th''': rewind tape at idFF (end of tape) | ||

| + | * '''Fruit Machine Simulator''': black screen blue border | ||

| + | * '''Fruit Machine Simulator II''': black screen, reboot | ||

| + | |||

| + | G-LOC R360, '''Galachip''' (space invaders), Galletron, Garfield 1 & 2, Gauntlet-Micropower, Gazza s Super Soccer, GBA Championship Basketball 2 On 2, '''Geasa-Parabola''', Gem, Geoff Capes Strongman, '''Ghost Hunters''', '''Ghostbusters 1''', Ghostbusters 2, Ghouls, Gilligan s Gold, Glass, '''Glen Hoddle Soccer''', Glider Rider, '''Golf Trophee''', Gorbaf El Vikingo, Graham Gooch s Test Cricket, '''Grand Prix 500cc''', Grand Prix Driver, Great Gurianos, Grell and Falla, Greyfell, '''Grid Trap''', Ground Zero, Guadalcanal, Guardian 2-Revenge of the mutants, Guerre des galaxies, Guerrero Espacial, Gunfighter | ||

| + | Galaxia, Game Over I - 1st., Gary Linekers s Superstar Soccer, Gauntlet II, Gems Of Stradus, Get Dexter 1 & 0, Go for Gold, Grand Prix, Grand Prix Simulator 2, Grand Prix Tennis, Grange Hill, '''Green Beret''', Gregory Loses His Clock, Guardian Angel | ||

| + | |||

| + | * '''Gabrielle''': Rewind tape | ||

| + | * '''Galactic Conqueror''': Rewind tape, idFF (end of tape) | ||

| + | * '''Galactic Games''': "LOADING: Please Wait" | ||

| + | * '''Galaxia SPANISH''': crash during play (when crashing on a wall : reboot) | ||

| + | * '''Galivan''': black screen | ||

| + | * '''Game Over II''': black screen orange border | ||

| + | * '''Gauntlet I-The Deeper Dungeon''': nothing displayed | ||

| + | * '''Gauntlet III''': welcome image, no proposition to change tape side. At end of first tape I insert the second one... Not loading the 3rd tape. | ||

| + | * '''Gauntlet''': reboot | ||

| + | * '''Gazza II''': "Loading error - Please retry" | ||

| + | * '''Gee Bee Air Rally''': return to BASIC | ||

| + | * '''Gemini Wings''': black screen pink border, id13 reboot | ||

| + | * '''Ghost n Goblins''': Rewind tape | ||

| + | * '''Gi Hero''': Searching 00 Loading 00...07 Rewind to 0C (to retry ?) | ||

| + | * '''Gilbert-Escape From Drill''': glitch, and then black screen | ||

| + | * '''Gladiator''': Rewind tape | ||

| + | * '''Golden Axe''': reboot id14 | ||

| + | * '''Golden Basket''': welcome image then reboot. | ||

| + | * '''Goliath-Le Defi''': problem during load of welcome image | ||

| + | * '''Golpe en la Pequena China''': no key | ||

| + | * '''Grand Prix Circuit''': tape stopped with strange id value : 00 | ||

| + | * '''Grand Prix Master''': blue screen | ||

| + | * '''Grand Prix Simulator 1''': idFF (end of tape) | ||

| + | * '''Great Courts''': blocked by a password | ||

| + | * '''Gremlins-The Adventure''': message "Resume a saved game ?" - no keyboard (same in WinAPE), version ripped in 2018 in CPC-Power does run fine. | ||

| + | * '''Gremlins 2''': reboot (Turbo Data + Standard Data) - running ok in WinAPE | ||

| + | * '''Gryzor''': reboot (Turbo Data + Pure Tone + Sequence of Pulses) | ||

| + | * '''Guillzemo Tell''': no keyboard, 4 Turbo Data, last one is big - running ok in WinAPE | ||

| + | |||

| + | Hacker 2, Halls of Gold, Happy Letters, '''Happy Numbers''', Happy Writing, Hard Drivin, '''Hard Hat Mack''', '''Harricana-Raid International Motoneige''', Harrier Attack, Haunted Hedges (pacman), Haunted House (txt), Havoc, Hawk Storm version 64K, Heartland, Heathrow International Air Traffic Control, Heavy on the Magick (txt), Helicoptero 2000, Heliot, Helvera-Mistress of the Park (txt), Herberts Dummy Run, Here and There With the Mr Men, '''Hero''', Hero of the Golden Talisman, Herobotix, Hexenkueche 1 & 2 (Cauldron), Hi-Q Quiz, Hi Rise, High Moon, '''Highier''', Hijack, '''HMS Cobra''', Hobgoblin (GNG), '''Hold-Up''', Holdfast, Hollywood Or Bust, Hollywood Palace, Home Runner, '''Hong Kong Phooey''', '''Hot Shot''', House of Usher, How To Be A Hero, Hunchback, '''Hundra''', Hunter Killer, Hustler, Hydrofool, '''Hyperbowl''', Hyperspace 4 (txt) | ||

| + | Hacker 1, Hammer-Head, Hammer boy, Hercule-Slayer Of The Damne, Heroes of the Lance,, Hideous, Humphrey, Hunchback 1, Hunchback 2, Huxley Pig, Hypsys | ||

| + | |||

| + | * '''Hammerfist''': white screen blue border, reboot while starting drawing welcome screen id13 | ||

| + | * '''Handicap Golf''': Rewind tape | ||

| + | * '''Hanse''': Rewind tape while loading welcome screen | ||

| + | * '''Hardball''': Rewind tape | ||

| + | * '''Harvey Headbanger''': id11 id11 '''id12''' id13 - Sequence of pulses of different length - id9C (crash) + Searching 00. Rewind to 0D | ||

| + | * '''HATE-Hostile All Terrain Encounter''': reboot | ||

| + | * '''Having Fits Of Madness''': BASIC 1.1 - to retest in 6128 model version. black screen green border. | ||

| + | * '''Head Over Heels''': black screen with message "LOADING: Please Wait" id11 id11 '''id12''' (Pure Tone) id13 (crash) | ||

| + | * '''Heavy Metal''': reset while loading welcome screen | ||

| + | * '''Helichopper''': id19 - Generalized Data Block. Rewind to 03 | ||

| + | * '''Hero Quest''': black screen, message "level 12" | ||

| + | * '''Heroes of Karn''': "LOADING ERROR" back to BASIC. | ||

| + | * '''High Steel''': id11 id11 '''id12''' id13 id70 (crash). Rewind to 0A | ||

| + | * '''Highlander''': message "LOADING: Please Wait" id11 id11 '''id12''' id00 (crash) | ||

| + | * '''Highway Encounter''': message "LOADING: Please Wait" id11 id11 id12 id00 | ||

| + | * '''Histo-Quizz''': Rewind tape (after loading a party) idFF (end of tape) | ||

| + | * '''Hive''': id13 id2E (crash). Rewind to 02 | ||

| + | * '''HKM-Human Killing Machine''': reboot after a count down | ||

| + | * '''Hockey''': idFF (end of tape), no keyboard | ||

| + | * '''Hopper Copper''': Rewind tape (to retry ?) | ||

| + | * '''Hoppin Mad''': Rewind tape (to retry ?) | ||

| + | * '''Hostages''': welcome screen and freeze (tape stopped), no keyboard | ||

| + | * '''Hot-Rod''': black screen pink border, reboot id14 | ||

| + | * '''How To Be A Complete Bastard''': white screen, blue border | ||

| + | * '''Hudson Hawk''': grey screen, pink border | ||

| + | * '''Hunter or Hunted''': Rewind tape | ||

| + | * '''Hybrid''': id13 id7F (crash) "Searching 00" | ||

| + | * '''Hydra''': black screen border blue | ||

| + | * '''Hyper Sports''': welcome screen, and then nothing | ||

| + | |||

| + | i alien, Ikari Warrior, Impossaball, Inca Curse - adventure B (txt), Indigestion, Indoor Soccer, Inertie, Infernal Runner, Inquisitor-Shade of Swords, Interchange, International Football, '''International Karate Plus''', International Manager, International Rugby, International Tennis, Into Oblivision, Into the Eagle s Nest, '''Invasion of the Zombie Monsters''', Invasores, Invierte y gana (manager), Invitation (txt), ISS-Incredible Shrinking Sphere, Iznogood | ||

| + | Ilogic All, '''Impossible Mission 1''', Impossible Mission 2, Indoor Race, Inside Outing, Invasion, Isoleur, Italian Supercar, Ivan Ironman Stewart s Super Off Road | ||

| + | |||

| + | |||

| + | * '''i Ball 2 - quest for the Past''': Rewind to 8 | ||

| + | * '''i Ball''': Rewind to 7 | ||

| + | * '''Ice Breaker''': reboot | ||

| + | * '''Imagination''': Rewind to 7 | ||

| + | * '''Impossamole''': "LOAD ERROR" level 1. A lot of id14 | ||

| + | * '''Indiana Jones 3''': black screen during second tape load | ||

| + | * '''Indiana Jones 4''': Please rewind | ||

| + | * '''Indiana Jones''': counter down : tape stopped in middle of id11 transmission, noise, reboot | ||

| + | * '''Infiltrator''': message "LOADING: Please Wait", glitch idFF (end of tape) idem second tape. | ||

| + | * '''Infodroid''': reboot | ||

| + | * '''Interdictor Pilot''': game not running - no key | ||

| + | * '''Interieur''': "Rewind tape", end of tape id=FF | ||

| + | * '''International 3D Tennis''': 64K version : reboot at begin of welcome image. | ||

| + | * '''International Karate''': reset to BASIC | ||

| + | * '''International Speedway''': rewind to 15 - great for comparative speed test :) | ||

| + | * '''It s a Knockout''': message "LOADING: Please Wait" id14 | ||

| + | * '''Italia 90 World Cup Soccer''': "WARNING" message, reboot | ||

| + | * '''Italy 1990''': game not launched despite of inserting face B | ||

| + | |||

| + | Jack and the beanstalk, Jack the Nipper II, Jackson City, Jail Break, Jammin, Jet-Boot Jack, Jet, Jet Set Willy-the final frontier (password needed), '''JetPac''', Jeux de Kim, Jigsaw Rescue, Jimmy Business, Jimmy s Soccer Manager, Jinks, Jocky Wilson s Compendium of Darts, '''Jocky Wilson s Darts Challenge''', Joe Blade I, Joe Blade II, Joe Blade III, Johnny Reb II, Jolly Poppa Down (txt), Jolly Roger s Dungeon Escape, Jonah Barringtons Squash, '''Jonny Quest''', Juggernaut, Jump, Jump Jet, Jumper, Jumpman, Jungle Warrior, Justin | ||

| + | Jack Nicklaus Golf, Jai Alai, | ||

| + | |||

| + | * '''Jack the Nipper I''': game not launched. xFF, still at welcome screen. | ||

| + | * '''Jackal''': grey screen, then reset | ||

| + | * '''Jahangir Khan World Championship Squash''': "Tape Loading error..." | ||

| + | * '''James Clavell s Shogun''': id11 6 times then '''id10''' | ||

| + | * '''James Debug dans Le mystère de l'Ile Perdue''': joystick misunderstood | ||

| + | * '''Jaws''': id11 4 times then '''id10''' - "Rewind to 04" | ||

| + | * '''Jet Bike Simulator''': id13 pure data, pure tone, loop | ||

| + | * '''Jet Set Willy II''': Rewind tape (all id11) | ||

| + | * '''Johnny Proot II''': Rewind tape (end of tape idFF, all id11) | ||

| + | * '''Jungle Jane''': blue screen, idFF (end of tape) | ||

| + | * '''Jungle Warfare''': game auto launched, no joystick/keyboard | ||

| + | |||

| + | K Y A, '''Kane''', Karl s Treasure Hunt, Kart 3000, Kat Trap, Ke Rulen Los Petas (txt), '''Kenny Dalglish Soccer Manager''', '''Kenny Dalglish Soccer Match''', Kentilla (txt), Kentucky Racing, Kick off II, '''Killapede''', Killer Cobra, Killer Gorilla, Killer Ring, King Leonard, Klax, Knight Ghost, Knight Lore, Knight Orc, Knight Tyme, Knightmare, Knights and Demons, Kobayashi Maru, Kokotoni Wilf, Kong s Revenge, Krakout, Kung-Fu Master, '''Kwik Snax''', KYA | ||

| + | Karnov, '''Kung-fu''' | ||

| + | * '''Kaiser''': Rewind tape | ||

| + | * '''Kettle''': reset id11, id13 not reached | ||

| + | * '''Kick off I''': Rewind tape | ||

| + | * '''Killed Until Dead Murder At Midnight''': id11, id11, (id12 id13) several times | ||

| + | * '''Kinetik''': "Rewind to 03" | ||

| + | * '''Knight Force''': Rewind tape | ||

| + | * '''Knight Games''': id13 | ||

| + | * '''Knight Rider''': id13 | ||

| + | * '''Konami s Golf''': id13 | ||

| + | * '''Kong Strikes Back''': id13 | ||

| + | * '''Kotoran s Shadow''': invalid CDT format | ||

| + | * '''Kristal''': Rewind tape | ||

| + | |||

| + | L'Affaire Sydney (txt), L'Affaire Vera Cruz (txt), L'Anneau de Zengara, L Hepiss, La Armadura Sacradda De Antiriad, La Aventura Original (txt), La Caza del Octubre Rojo, La Chose De Grotemburg (txt), La course a la boussole, La foret Infernale, La France, La Geste D Artillac (txt), La Guerra de las Vajillas (txt), La Trilogie du temple d Apshai, La Ville Infernale, Labyrinth Hall (txt), Langolo del Diavolo, Las Joyas Del Nio, Las Vegas Video Poker, '''Laser''', Laser Blast, Laser Tiempo, Le 5eme Axe, Le Bagne De Nepharia (txt), Le Diamant de l Ile Maudite (txt), Le jeu du Roy, Le Millionnaire, Le spectre d'Anubis (txt), Le Survivant, Le Talisman d Osiris, Le Tour du Monde en 80 jours (txt), Le Tournoi du Siecle, '''Le Tresor de l Amazone''', League Challenge, Legend, Lenguaje, Les aventures du KA-Menace sur l Arctique, '''Les Diamants de la Peur''', Lettura Rapida, Life Expectancy Zero, Lifeterm (txt), '''Light Force''', Linkword-French, Logiformes, Lop Ears, Lords, Lords of time (txt), Lorna, Los Angeles Swat, Los Pajaros De Bangkok (txt), Los Planetas-El Sistema Solar, Los Templos Sagrados (txt), '''Lost Caves and the Tomb of Doom''', Loto, Lotus Turbo Esprit, Lucky Fruits | ||

| + | L Heritage-Panique a Las Vegas, Lee Enfield Space Ace, Little Puff in Dragonland, Lords of Chaos | ||

| + | * '''L oeil de Set''': rewind tape | ||

| + | * '''La Abadia del crimen''': blue screen and grey border | ||

| + | * '''La Malediction de Thaar''': rewind tape idFF | ||

| + | * '''La Tour Fantastique''': rewind tape | ||

| + | * '''Lala Prologue''': black screen | ||

| + | * '''Las Vegas Casino''': Read error B (too quick) | ||

| + | * '''Last Duel''': count down, reset | ||

| + | * '''Last Ninja 2''': glitch, id14 reboot | ||

| + | * '''Le Necromancien''': red screen, blue border | ||

| + | * '''Leader Board''': id12 freeze | ||

| + | * '''LED Storm''': black screen, rewind at start of block. | ||

| + | * '''Lemmings''': no welcome image | ||

| + | * '''Les aventures de Jack Buron-big troube in little china''': no keyboard | ||

| + | * '''Les Joyaux de Babylone''': "ERREUR CASSETTE" | ||

| + | * '''Leviathan''': reset at id14 | ||

| + | * '''Line of Fire''': inserting second side does nothing | ||

| + | * '''Live and Let Die''': black screen idFF (end of tape) | ||

| + | * '''Living Daylights''': same problem than in dsk version | ||

| + | * '''Lords of Midnight''': welcome image, then freeze | ||

| + | |||

| + | Mach 4, '''Mach 3''', Macrocosmica, Mad Mix Game, Mad Mix Game 2, Magic Clock, '''Magical Drop CPC''', Manager, Mansion Kali 1 (txt), Mansion Kali 2 (txt), Mantis 1 (txt), Mantis 2 (txt), Mapa del Cielo, Master Chess, Match Point, Mathasard, Mathe Stunde 1, Max, Meltdown, Mercenaire, Mexico 86, Minas, Misil Atack, Missile Ground Zero, Missiles, Molecule Man, Money Molch, Monster of Murdac, Monty Mutant, '''Monument''', Mordon s Quest (txt) | ||

| + | Mariano The Dragon In Capers In Cityland, Marius Tresor Foot, Masters of the Universe, Mathex n1, Maziacs, Megacorp, Meganova, Message from Andromada (txt), Miami Cobra GT, Microprose Soccer | ||

| + | * '''M enfin''': sound freeze during welcome picture | ||

| + | * '''Mahjong''': Rewind tape | ||

| + | * '''Manic Miner''': crash after loosing one time. | ||

| + | * '''Mansion''': Rewind tape during first mission | ||

| + | * '''Marble Madness-Deluxe Edition''': blue screen | ||

| + | * '''Marsport''': password | ||

| + | * '''Master of the lamps''': Rewind tape | ||

| + | * '''Matchday 2''': black screen blue border | ||

| + | * '''Mercenary Escape from Targ''': welcome screen, no keyboard | ||

| + | * '''Mercs''': reboot | ||

| + | * '''Metropol''': back to basic at first round of play | ||

| + | * '''Miami Vice''': | ||

| + | * '''Michel Futbol Master Super Skills''': reboot | ||

| + | * '''Mickey Mouse''': reboot | ||

| + | * '''Micro Sapien''': Rewind tape | ||

| + | * '''Mike Head S Computer Pop Quiz''': menu without keys | ||

| + | * '''Mineur''': Read error a | ||

| + | * '''Mobile Man''': reboot | ||

| + | * '''Monopoly''': grey screen | ||

| + | * '''Montsegur''': reboot | ||

| + | * '''Moonblaster''': game not launched | ||

| + | |||

| + | |||

| + | |||

| + | * * '''Breaking Baud.cdt''': no pause, last part "pink floral" heart is missing. As explain at begin of demo, instructions are executed during they are written in memory, speed of tape against speed of Z80... | ||

| + | |||

| + | ===On ZX-Uno FPGAmstrad version=== | ||

| + | Games that doesn't run are : | ||

| + | * '''adios_a_la_casta.dsk''': bad sound. Does pass hacking memory banks this way : | ||

| + | else b"1100" when RAMbank="100" and (A(15)='0' and A(14)='1') | ||

| + | else b"1101" when RAMbank="101" and (A(15)='0' and A(14)='1') | ||

| + | else b"1110" when RAMbank="110" and (A(15)='0' and A(14)='1') | ||

| + | else b"1111" when RAMbank="111" and (A(15)='0' and A(14)='1') | ||

| + | else b"10" & A(15 downto 14); -- default value | ||

| + | * '''Ghouls'n'Ghost.dsk''': black screen during game. RAM is not relaxed enought to permit changing address just after knowing if Z80 does a read or a write (ROM written=> does write on RAM hidden behind) | ||

| + | |||

| + | * '''jdva6.dsk''': no keyboard... [https://github.com/renaudhelias/RubikCubePaletteCPC/tree/master/JDVA%236_test JDVA#6 test] | ||

| + | |||

| + | Antonio Villena mail "ZXDOS conversion of your CPC core" 2019/01/29 | ||

| + | Hi Renaud | ||

| + | It's for asking if you plan a conversion of your CPC core for this platform. It's like ZX-Uno, but with: | ||

| + | -A bigger FPGA, LX16 instead LX9. | ||

| + | -18 bit DAC | ||

| + | -32Mb of SDRAM, also 512K of SRAM | ||

| + | -dual joystick port | ||

| + | -Separate PS/2 joystick and mouse | ||

| + | If you are interested I can provide the two addon boards, so you only need the LX16 board. Bought from Aliexpress is about 18 EUR. | ||

| + | https://es.aliexpress.com/store/product//606998_32818384452.html | ||

| + | Regards | ||

| + | |||

| + | == Effort done == | ||

| + | === VGA === | ||

| + | Pixels and VRAM. Palette and rasters. CRTC0 | ||

| + | ==== VGA: CRTC0 ==== | ||

| + | CRTC0 seems the best one, some demo does cry when detecting a poor CRTC1 (CRTC1 seem a low cost version of CRTC0). I have to implement a CRTC0 instead of my current CRTC1... | ||

| + | |||

| + | In fact CRTC1 is the best one. CRTC2 is the low cost version. CRTC0 did appears before CRTC1. | ||

| + | |||

| + | Some demos are running only on CRTC0 and others CRTC1. | ||

| + | |||

| + | Done in r005.8.14. Detected as CRTC0 by WakeUp! - "Enjoy the show" message displayed. | ||

| + | |||

| + | In r005.8.15. WakeUp! (CRTC0/MEM_wr quick) detected as Emu first time, and after a quick reset, does say detected as CRTC0. | ||

| + | |||

| + | In ZX-Uno FPGAmstrad, I implemented CRTC0. | ||

| + | |||

| + | CRTC1 has double sized VSYNC against CRTC0 (moustache test) | ||

| + | |||

| + | ==== VGA: VRAM ==== | ||

| + | ram_palette. | ||

| + | |||

| + | VRAM contains 800x300 amstrad pixels (VZoom x2), displayed VGA 800x600@72Hz with fix regular border at 768×576 and fix inside border at 768×544. | ||

| + | |||

| + | In ZX-Uno, VRAM contains 800x300 amstrad pixels (VZoom x2), displayed 640x480@60Hz, with vertical only border. | ||

| + | |||

| + | * simple_GateArrayInterrupt.vhd (GA to VRAM) parameters : VRAM_Hoffset/VRAM_Voffset | ||

| + | * aZRaEL_vram2vgaAmstradMiaow.vhd (VRAM to VGA) parameters : H_BEGIN/H_END/V_BEGIN/V_END (theorical fixed values) | ||

| + | To calibrate : VRAM_Hoffset++ does offset one char left. VRAM_Voffset++ does offset one line up. On display H_BEGIN does begin to scan lines of VRAM. But V_BEGIN does not enter in consideration here : vertical=0 does begin to scan columns of VRAM. | ||

| + | |||

| + | In original CPC, top border has 1/2 char more than bottom border. I used Batman Forever default welcome/calibration screen to calibrate VRAM offsets. On ZX-Uno I used Arkanoid to calibrate VRAM offsets. | ||

| + | |||

| + | RAM_palette contains the ink list and the mode for each line of VRAM, sampled at horizontal middle of 800x600 screen, and used at begin of each line. | ||

| + | |||

| + | ==== VGA: TODO : arnoldemu testbench ==== | ||

| + | '''arnoldemu testbench: crtctest''' | ||

| + | |||

| + | Adding choice of CRTC 0 or 1 on OSD, and passing this test could be great. | ||

| + | |||

| + | ==== VGA: TODO : winape testbench ==== | ||

| + | '''winape testbench: plustest''' | ||

| + | |||

| + | a better border heuristic | ||

| + | |||

| + | Using winape testbench (plustest), test 2 does show somes problems while border does go out of screen, negative border does hide line itself. | ||

| + | |||

| + | === bootloader === | ||

| + | SDCARD and RAM. | ||

| + | |||

| + | (nothing to say here, really ???) | ||

| + | |||

| + | === GA === | ||

| + | |||

| + | ==== GA: alignment of HSYNC Interrupt ==== | ||

| + | Interrupt are respected since version "candidate 001" of FPGAmstrad, Markus does help me a lot about it. | ||

| + | |||

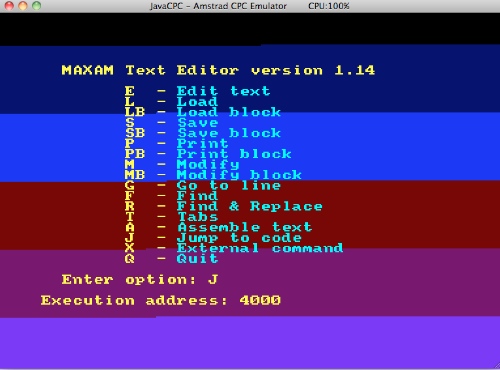

| + | [[File:JavaCPC_running_norecess.jpg]] | ||

| + | |||

| + | JavaCPC running norecess's "using-interrupts" code [[http://norecess.cpcscene.net/using-interrupts.html]] | ||

| + | |||

| + | It could be interesting to test this asm code on next version of FPGAmstrad. | ||

| + | |||

| + | ==== GA: Sniffing of a real Amstrad ==== | ||

| + | [[File: cpc_plus_m1.jpg]] | ||

| + | Code name: Raptor | ||

| + | |||

| + | I listen to some wires of my Amstrad CPC 6128 plus, but I can't access VSYNC/HSYNC output of CRTC, so I have to buy another model in order to do this test. In fact you can listen at clock of Amstrad and transmit it to FPGA DCM component, resulting a accelerated clock sequence, that's it, with FPGA DCM you can overclock output Amstrad clock signal in order to insert more operations, I use this tip for listening signals and save them inside starter kit asynchronous RAM (write, stop write, write, stop write... I’m a perfectionist paranoid...) | ||

| + | |||

| + | You can power Amstrad CPC using extension port, applying 5v. By doing it, power down button of Amstrad doesn’t run. Using this way you reach a common 5v power between starter-kit and Amstrad. I connected wires from extension port directly to FPGA, as they are used just for listening. | ||

| + | |||

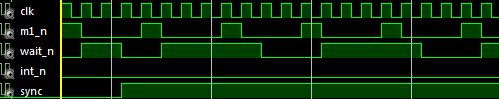

| + | ==== GA: WAIT_n generator - currently in r008.5.14 ==== | ||

| + | Instruction timing. | ||

| + | |||

| + | I tested instruction timing of [[T80]] compare to instruction timing of JavaCPC emulator. I deduce synchronization of Z80 with CRTC on M1 signal by WAIT_n insertion in order to have a multiple of 4 Tstates per instruction. I deduce also one WAIT_n inserted during MEM_WR operation (yes I log testbench [[T80]], I’m crazy) | ||

| + | |||

| + | I just made a test bench log of [[T80]] (log of instruction's M1, and first M1 coming after knowing that I send a lot of NOP after my instruction), and compare it to a JavaCPC timing array. Some instructions was not tested (interrupt wait, and special timing (instructions with change timing)), but all others passed correctly. | ||

| + | |||

| + | MEM_WR has an OSD menu choice to switch between "quick" and "slow", "slow" mode does insert ONE WAIT_n during detection of MEM_WR. This switch exists because somes games are running in "slow" mode and others in "quick" mode. | ||

| + | |||

| + | An elegant fork by Sorgelig, sum up nicely the "MEM_WR:slow" algorithm + the HACK_Z80 flag of r008.5.14 : | ||

| + | T80pa CPU | ||

| + | ( | ||

| + | (...) | ||

| + | .cen_p(ce_4p & (WAIT_n | no_wait)), | ||

| + | .wait_n(1) // (cyc1MHz | (IORQ_n & MREQ_n) | no_wait) | ||

| + | ); | ||

| + | // Current WAIT_n generation is not correct! | ||

| + | // It should use WAIT_n instead (see commented out code above ^^) | ||

| + | reg WAIT_n; | ||

| + | wire acc = (MREQ_n | ~RFSH_n) & IORQ_n; | ||

| + | always @(posedge clk) begin | ||

| + | reg old_acc; | ||

| + | if(ce_4p) begin | ||

| + | old_acc <= acc; | ||

| + | if(old_acc & ~acc) WAIT_n <= 0; | ||

| + | if(cyc1MHz) WAIT_n <= 1; | ||

| + | end | ||

| + | end | ||

| + | |||

| + | ==== GA: WAIT_n generator - talk about r008.5.14 ==== | ||

| + | |||

| + | In fact it exists several instruction making MEM_wr, and adding each one ONE WAIT_n does result in different case of synchronization. | ||

| + | |||

| + | [http://www.cpcwiki.eu/forum/emulators/cpc-z80-timing/ CPC Z80 timing] | ||

| + | |||

| + | If it's about managing GA reading pixels, perhaps not only M1 signal are synchronized but also the MEM_RD and MEM_WR accesses at another offset. | ||

| + | |||

| + | [http://amstrad.eu/modules/newbb/viewtopic.php?post_id=24592 Timings instructions Z80 sur CPC] | ||

| + | |||

| + | If interruption r52 is regular, even while making a continues MEM_WR, interruption (int<='1') shall be taken into account above WAIT_n insertions ? | ||

| + | |||

| + | In Z80 sequence diagram, an IO_ACK(+M1) is preceded by M1 (single) | ||

| + | |||

| + | cpctest.dsk -Timing Instruction- is different while using mode "MEM_WR=slow" and "MEM_WR=quick". Strangly better using "MEM_WR=quick". | ||

| + | |||

| + | Current version is using "Z80_HACK=true" (parameter set during compilation), that shunt Z80.WAIT_n entry, Z80.clock is slow down during theses WAIT_n. It's the only current way I succeed in slowing down enough Timing Instruction for unlocking Saboteur 2 game. | ||

| + | |||

| + | Key games here are : Saboteur 2 (run fine with "MEM_WR=slow", does freeze with "MEM_WR=quick") and Arkanoid II (run fine with "MEM_WR=quick", too slow using "MEM_WR=slow") | ||

| + | |||

| + | [http://www.cpcwiki.eu/forum/programming/cpc-z80-commands-and-how-long-they-take/40/ CPC Z80 Commands and how long they take...] | ||

| + | |||

| + | ==== GA: WAIT_n generator - plustest-5 - Tests on real CPC (by DanyPPC) ==== | ||

| + | [http://www.cpcwiki.eu/forum/amstrad-cpc-hardware/need-plustest-dsk-testbench-5-output-on-original-cpc-6128/ CPCWiki's forum : Need plustest.dsk testbench 5 output on original CPC 6128] | ||

| + | |||

| + | So 2A is really during 5 NOPs... perhaps MEM_rd has to be slow down with one WAIT_n like for MEM_wr. Perhaps in this case 5T's instruction has not to be slow down. I have to fork r005.8.16c3 to test that. - update : in schematic GateArray does not has "MEM_wr wire" (but MEM_req and RD, so can deduce WR, but in an evil brain's way) - update 2 : all tests failed except one in testbench using this way, perhaps because RFSH_n does also use MREQ_n during M1 cycle. Perhaps WAIT_n generator can detect the current OP Code fetched (this is conform to [http://www.google.com/patents/US5313621 Patent US5313621 : Programmable wait states generator for a microprocessor and computer system utilizing it ]). - update : principe of concept validated for one instruction (2A), I can slow down instructions one per one, I don't know why I had to insert two WAIT_n instead of one here, but its results a plustest.dsk testbench with 2A instruction validated, that's done on r005.8.16c5f5 (candidate 5 fork 5), but I have to revert it to r005.8.16c3f5 I think before going further. | ||

| + | |||

| + | About testbench border effects, I think that IO_ACKed instructions has to be under same rules (MEM_wr, modulo 4 etc) - update : same result in testbench using this way. | ||

| + | |||

| + | ==== GA: WAIT_n generator - plustest-9 - Tests on real CPC (by GUNHED and Kris) ==== | ||

| + | [http://www.cpcwiki.eu/forum/amstrad-cpc-hardware/need-plustest-dsk-testbench-9-output-on-original-cpc-6128/ CPCWiki's forum : Need plustest.dsk testbench 9 output on original CPC 6128] | ||

| + | |||

| + | GUNHED results : | ||

| + | System 1: CPC6128, CRTC2: | ||

| + | Test 9 works normal until the &EC codes, there are two errors marked with an "X". | ||

| + | &ED, &46: 2 | ||

| + | &ED, &4E: 2 | ||

| + | After &ED, &5D it suddenly stops working! | ||

| − | + | System 2: 6128 Plus: | |

| + | &ED, &46: 2 | ||

| + | &ED, &48 5 | ||

| + | &ED, &49: 5 | ||

| + | &ED, &4E: 2 | ||

| + | &ED, &50: 5 | ||

| + | &ED, &51: 5 | ||

| + | &ED, &58: 5 | ||

| + | &ED, &59: 5 | ||

| + | After &ED, &5D it suddenly stops working! Probably a crash, since a spot appears on screen. | ||

| + | Kris results : | ||

| + | Here are my results (teste performed on CPC 6128 CRTC 1) | ||

| + | Pictures of each screen attached in the .rar file. | ||

| + | (...) | ||

| + | In pictures of Kris, after ED5D, it does stop also. Only ED test part has some failings : | ||

| + | * ED46:C | ||

| + | * ED4E:C | ||

| + | In WinAPE (by default CPC 6128 CRTC1), ED test does finish its screeen result, with several fails : | ||

| + | * ED46:2 | ||

| + | * ED4E:2 | ||

| + | * ED66:2 | ||

| + | * ED6E:2 | ||

| + | Others screens results after does pass. Relaunching once again in WinAPE, same results. | ||

| − | + | ==== GA: WAIT_n generator - RET cc and WAIT_n timing analysis ==== | |

| + | IO_ACK offset into INT (interrupt) should not implicated by WAIT_n generator, and it seems that a WAIT_n during T2 is ignored because of autowait already inserted at this moment... for synchronizing an IO_ACK, I have normaly to insert WAIT_n during T2+2. No way, instruction itself is synchronized, so IO_ACK is synchronized also, you don't have to insert WAIT_n during T2+2. | ||

| − | + | http://www.cpcwiki.eu/forum/emulators/cpc-z80-timing/ : ~ a WAIT_n does not use RAM access, so does not slow down a "CPC instruction" (hypothesis) - but what about an IO_ACK during NOP in this case ? | |

| + | In doc, IO_ACK begin after T2, during the two autowait inserted. So no way to detect that an instruction is IO_WAITing before slowing it following "slow down" instruction timing table. | ||

| + | http://www.cpcwiki.eu/forum/programming/cpc-z80-commands-and-how-long-they-take/30/ | ||

| + | So, it's more correct to not think of it stretching the M cycle, but instead not starting the next one that requires | ||

| + | a memory access until the 4th cycle. | ||

| + | |||

| + | If you think of it like this, it also explains the weird exception that happens for interrupt handling. | ||

| + | Normally, responding to an interrupt adds 1us on the CPC. That's because it actually just adds 2 T states for the interrupt | ||

| + | acknowledge before the next instruction fetch. However, in case where the last M cycle takes 6 T states, the interrupt | ||

| + | acknowledge doesn't delay the instruction prefetch and so the usual 1us delay doesn't occur. | ||

| + | |||

| + | "Simples!" - ralferoo | ||

| + | (4T equals 1us equals 1 NOP => modulo 4 synchronization of M1) | ||

| + | |||

| + | So you slow down instructions following a slowing down instruction table, slowing it the less you can, and then IO_ACK comes or not, and then you synchronize next M1 putting WAIT_n during T2 modulo 4. IO_ACK two autowaits are not prolongated. | ||

| + | |||

| + | ralferro explains also that stretching instruction timing depends of memory used or not by instruction. I know that Amstrad schematics does not use the MEM_WR wire. So it could be hard to deduce if they added 1 or more WAIT_n for certain instructions. But I'm more about 1 WAIT_n inserted at maximum each time (it's more easy to hard implements), and the modulo 4 synchro, let's see results of my current experiment (comparing time instruction of Z80 and plustest.dsk testbench, deducing diff table of "slowing down instructions") | ||

| + | |||

| + | ==== GA: WAIT_n generator - talk about r005.8.16 ==== | ||

| + | OSD menu has now "WAIT_n:slow|quick", a WAIT_n generator is implemented adding 0, 1 or 2 WAIT_n per instruction. | ||

| + | |||

| + | I revisited the edges of WAIT_n generator, to insert WAIT_n at 2T (like explain in Z80 doc), so normaly it is retro-compatible with official T80. Doing this way I can set HACK_Z80 flag at false (T80.WAIT_n is now used in r005.8.16) | ||

| + | |||

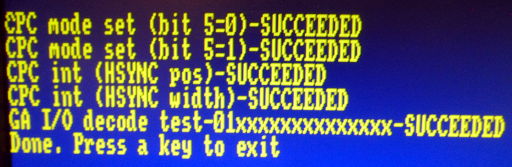

| + | I also removed the edge detection of IO_ACK on gatearray, replacing it by state detection of IO_ACK, resulting cpctest's testbench back : this test of HSYNC width is now successfull. | ||

| + | |||

| + | plustest.dsk has some "missing tests" but in fact there are the prefixes : CB, DD, ED, FD, used to launch other areas of instructions. | ||

| + | |||

| + | HALT is the only one instruction that will be always OK on plustest.dsk instruction timing testbench. As this instruction cannot be timed. | ||

| + | |||

| + | plustest.dsk testbench 5 does pass, except for two instruction : CPIR and CPDR - btw, in r005.8.16, its instructions are using then same "WAIT_n generator" slower than CPI/CPD : none (no WAIT_n added for theses instructions) | ||

| + | |||

| + | ==== GA: WAIT_n generator - plustest.asm ==== | ||

| + | About 22 pages of source code using 3 columns per page. | ||

| + | .stdinst | ||

| + | (launch tests on several list of instruction, some instructions are tested differently using test functions : normtest, testit (testdjnz), rsttest...) | ||

| + | |||

| + | ld a,#c7 | ||

| + | call rsttest | ||

| + | => C7 RST 0H 4 3 | ||

| + | |||

| + | ld a,#cf | ||

| + | call rsttest | ||

| + | => CF RST 8H 4 3 | ||

| + | rsttest seems a nice candidate to explore, as all its tests are failing here. | ||

| + | |||

| + | .times1 | ||

| + | (CPC Timing array (first instruction set)) | ||

| + | |||

| + | ==== GA: TODO : arnoldemu testbench ==== | ||

| + | '''arnoldemu testbench: cpctest''' | ||

| + | |||

| + | [http://www.cpcwiki.eu/forum/emulators/amstrad-cpc-%27acid%27-test/ forum : amstrad cpc "acid" test] => ''I have uploaded updated tests : [http://cpctech.cpc-live.com/test.zip http://cpctech.cpc-live.com/test.zip]'' | ||

| + | |||

| + | Tests done here : ppi/psg/cpctest. | ||

| + | |||

| + | [[File:arnoldemu_testbench_CPCTEST-r005-6.png]] | ||

| + | |||

| + | In r005.6, I reach successfully some arnoldemu tests to calibrate more efficiently HSYNC interrupt : ppi.bin, psg.bin, cpctest.bin. | ||

| + | |||

| + | Games unlocked by r005.6 : Sigma7, Pac-land, Golden Tail. | ||

| + | |||

| + | In r005.8, Prehistorik is running fine. | ||

| + | |||

| + | In r005.8.4, arnoldemu testbench "cpctest" does fail :/ | ||

| + | |||

| + | In r005.8.7, arnoldemu testbench "cpctest" is OK | ||

| + | |||

| + | In r005.8.14 version, using default mode "MEM_wr:quick", is OK. And Prehistorik II is running fine. | ||

| + | |||

| + | In r005.8.16c29, arnoldemu testbench "cpctest" is OK (but it is a wip version :p) | ||

| + | |||

| + | ==== GA: TODO : MODE row buffer ==== | ||

| + | MODE does change at each begin of lines, not at begin of pixel drawn. | ||

| + | Il ne faudrait pas penser que l'on puisse changer de mode plusieurs fois par ligne. En effet. c'est "impossible"! (jusqu'à preuve du contraire, le mode s'enclenche à chaque synchro horizontale (HBL). | ||

| + | https://cpcrulez.fr/coding_logon35-le_gate_array.htm | ||

| + | |||

| + | ==== GA: Moustache testbench ==== | ||

| + | A homemade Testbench done firstly for helping Sorgelig to calibrate it's port of FPGAmstrad into MiSTer. But as Sorgelig core does run finer than mine (Pinball Dreams did pass ! WAIT_n:slow, CRTC 1, Brand name: Amstrad), I do then take back the good behavior using this testbench, resulting r005.8.16.1 | ||

| + | |||

| + | It's a stress testbench around VSYNC/HSYNC/interrupt. | ||

| + | |||

| + | If the cat doesn't catch the line, this testbench does fail (that's a small palette testbench). First array is about VSYNC length comparable between a real CPC and an emulator. Second array is about interrupt length. Stress is done by inserting NOP, NOPNOP, NOPNOPNOP or else NOPNOPNOPNOP instruction before each measure. | ||

| + | |||

| + | [https://github.com/renaudhelias/RubikCubePaletteCPC/blob/master/JDVPA%236_test/jdvpa6_moustache.dsk jdvpa6_moustache.dsk] | ||

| + | |||

| + | [[File:Jdvpa6 moustache-FPGAmstrad testbench.png|thumbnail|jdvpa6_moustache.dsk testbench]] | ||

| + | |||

| + | ==== GA: Sorgelig formula ==== | ||

| + | GA instruction-timing formula (compteur1MHz is 4MHz mod 4): | ||

| + | --Sorgelig formula : .wait_n((phase == 0) | (IORQ_n & MREQ_n) | no_wait) | ||

| + | if compteur1MHz > 0 and (IO_REQ_R='1' or IO_REQ_W='1' or MEM_RD='1' or MEM_WR='1') then | ||

| + | WAIT_n<='0' | ||

| + | I put it inside OSD menu WAIT_n:quick in r005.8.16.8.5c1 | ||

| + | Does pass easily plustest.dsk test 5, but not 9. Mister Amstrad does pass test 9, I misunderstood how its Z80 is hacked. | ||

| + | |||

| + | Another great Sorgelig formula btw : | ||

| + | -- Sorgelig formula : wire acc = (MREQ_n | ~RFSH_n) & IORQ_n; | ||

| + | MREQ<=not(MREQ_n or not(RFSH_n)); | ||

| + | |||

| + | === Z80 === | ||

| + | Architecture of Z80. | ||

| + | |||

| + | |||

| + | ==== Z80: test of a real Zilog 80 ==== | ||

| + | [[File:Z80fx2bb.jpg]] | ||

| + | Code name : Z80fx2bb, real Z80@2MHz (instead of 4MHz) on fx2bb extension card. | ||

| + | |||

| + | [[http://www.youtube.com/watch?v=YYnvkR5v3D0 http://www.youtube.com/watch?v=YYnvkR5v3D0]] | ||

| + | |||

| + | For it I plug all wires simply from 1 to 40. Some wires are cut, some are Vcc, others GND. Z80 output are directly connected, Z80 input are pull-up with red-red-red resistors (I like red), Z80 is powered 5v (pmod can give 5v using jumper). In fact z80 is so old component that powering it 5v does output 3.3v. | ||

| + | |||

| + | In fact the only difference between [[T80]] of opencore and real Z80 is that [[T80]] runs on rising_edge, and Z80 runs during low state. Test past with little modification of sequencer forcing it to do nothing during low state of z80, resulting a downclock (memory is too overclocked with this sequencer modification), perhaps using buffer on address bus and data bus could solve this detail... but as it runs for me it is not a problem. | ||

| + | |||

| + | ==== Z80: architecture ==== | ||

| + | ===== a) T80.vhdl ===== | ||

| + | 17 pages of source codes to read. | ||

| + | |||

| + | Not analyzed yet completly. | ||

| + | |||

| + | Contains the main workflow of Z80: current MCycle and its current TState. | ||

| + | |||

| + | Contains T80_ALU.vhdl and T80_MCode.vhdl components. | ||

| + | |||

| + | ===== b) T80_ALU.vhdl ===== | ||

| + | 6 pages of source codes to read. | ||

| + | |||

| + | Not analyzed yet completly. This analyse can certainly be wrong : wip. | ||

| + | |||

| + | Contains flags : C N P X H Y Z S | ||

| + | C : carry - set if result did not fit in the register | ||

| + | N : negative? - last instruction was substract | ||

| + | P : parity or overflow - overflow example : signed, 7F+7F=FE with overflow setted | ||

| + | X : undocumented | ||

| + | H : half carry - set if 4bit first bits of result did not fit in the register | ||

| + | Y : undocumented | ||

| + | Z : zero - set if result is zero | ||

| + | S : sign - it is an input ? | ||

| + | Contains ALU_Op : [ADD ADC SUB SBC AND XOR OR CP] ROT BIT [SET RES] DAA | ||

| + | |||

| + | ALU_Op is the basic instructions of Z80 coded here. T80_ALU.vhdl is a slave, a service exposed to T80_MCode.vhdl throw T80.vhdl | ||

| + | |||

| + | [[http://www.z80.info/decoding.htm § Disassembly tables]] shall make a cool ALU_Op quick reference card, doesn't it ? | ||

| + | |||

| + | ===== c) T80_MCode.vhdl ===== | ||

| + | First 5 pages, and last 2 pages of source codes to read. Others pages are "always the same" architectually speaking. | ||

| + | |||

| + | Not analyzed yet completly. This analyse can certainly be wrong : wip. | ||

| + | |||

| + | Gives instructions lengh : MCycles, TStates (please remark the 's' at end of theses words...), in [[http://www.zilog.com/docs/z80/um0080.pdf Z80 doc]] each instruction is timing described using "M Cycles" and "T States" vocabulary. | ||

| + | |||

| + | It's a "controler" (proof : you have some Set_*_To outputs), does gives orders to T80_ALU.vhdl throw T80.vhdl | ||

| + | |||

| + | Actions of this controler are : | ||

| + | * ALU_Op : the action ! | ||

| + | * I_DJNZ I_CPL I_CCF I_SCF I_RETN I_BT I_BC I_BTR I_RLD I_RRD I_INRC : actions not for ALU (wiring input/ouput, changing flags...) | ||