| (7 intermediate revisions by 2 users not shown) | |||

| Line 2: | Line 2: | ||

The [[ECB Bus]] connector of the board is intended to be plugged into the [[Schneiderware Basisplatine]], but it could be also wired directly to the CPCs Expansion Port. | The [[ECB Bus]] connector of the board is intended to be plugged into the [[Schneiderware Basisplatine]], but it could be also wired directly to the CPCs Expansion Port. | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

== I/O Ports == | == I/O Ports == | ||

{|{{Prettytable|width: 700px; font-size: 2em;}} | {|{{Prettytable|width: 700px; font-size: 2em;}} | ||

| − | |Address (default | + | |Address (default) || Usage |

|- | |- | ||

| − | |DFxxh | + | |DFxxh || Schneiderware RAM/EPROM - [[Upper ROM Bank Number|Expansion ROM bank number]] (W)<br>Battery-backed SRAM and/or EPROM are selected when the bank-number matches the jumper-selected values; the memory is then mapped to C000h..FFFFh (in case of READing one must also enable upper ROM via Gate Array). The bank number decoding is a bit strange: |

* EPROM/Read bank: All 8 bits decoded (bank 00h..FFh) | * EPROM/Read bank: All 8 bits decoded (bank 00h..FFh) | ||

* SRAM/Read bank: Only lower 4 bits decoded (bank X0h..XFh) | * SRAM/Read bank: Only lower 4 bits decoded (bank X0h..XFh) | ||

| Line 23: | Line 15: | ||

|- | |- | ||

|} | |} | ||

| + | |||

| + | '''Note''' - Port DFxxh is the standard [[Upper ROM Bank Number]] register, which is also used by [[AMSDOS]], for example. Reserved banks are 00h=Basic, and 07h=AMSDOS. Bank FFh (and XFh) can be also considred as reserved (as it's used by the "128K RAM detection" in CP/M+). Other bank numbers can be used by one (or more) Schneiderware Pseudo ROM board(s). | ||

== Pictures == | == Pictures == | ||

| Line 29: | Line 23: | ||

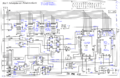

File:Schneiderware SRAM and EPROM Schematic.png|SRAM/EPROM Schematic | File:Schneiderware SRAM and EPROM Schematic.png|SRAM/EPROM Schematic | ||

</gallery> | </gallery> | ||

| + | |||

| + | == Software == | ||

| + | |||

| + | The magazine article contains three listings with examples on how to use the Pseudo ROM board, including a ROM version of the [[Schneiderware Real Time Clock]] driver. | ||

| + | |||

| + | == Scanned Article == | ||

| + | |||

| + | * [[Media:Schneiderware 8 - Pseudo ROM.pdf|Schneiderware 8 - Pseudo ROM.pdf]] - SRAM and EPROM mapped as ROM - '''4/1987 page 26-34''', plus corrections in 5/1987 page 32-34 | ||

| + | |||

| + | [[Category:Peripherals]] | ||

Latest revision as of 03:20, 29 August 2014

The Schneiderware Pseudo ROM is a expansion "ROM" board, with 16K EPROM (read-only) and 16K battery-backed SRAM (read/write-able), published by german magazine CPC Schneider International as part of their Schneiderware DIY series. The plain PCB, or the fully assembled board were also available via mail-order.

The ECB Bus connector of the board is intended to be plugged into the Schneiderware Basisplatine, but it could be also wired directly to the CPCs Expansion Port.

I/O Ports

| Address (default) | Usage |

| DFxxh | Schneiderware RAM/EPROM - Expansion ROM bank number (W) Battery-backed SRAM and/or EPROM are selected when the bank-number matches the jumper-selected values; the memory is then mapped to C000h..FFFFh (in case of READing one must also enable upper ROM via Gate Array). The bank number decoding is a bit strange:

The SRAM/Write mode doesn't disable the internal RAM in the CPC, so writes are going both to SRAM and normal RAM at C000-FFFF, that no matter if upper ROM is enabled/disabled via Gate Array; the author recommended to map VRAM to 4000-7FFF via CRTC registers, in order to prevent video dirt during writing. |

Note - Port DFxxh is the standard Upper ROM Bank Number register, which is also used by AMSDOS, for example. Reserved banks are 00h=Basic, and 07h=AMSDOS. Bank FFh (and XFh) can be also considred as reserved (as it's used by the "128K RAM detection" in CP/M+). Other bank numbers can be used by one (or more) Schneiderware Pseudo ROM board(s).

Pictures

Software

The magazine article contains three listings with examples on how to use the Pseudo ROM board, including a ROM version of the Schneiderware Real Time Clock driver.

Scanned Article

- Schneiderware 8 - Pseudo ROM.pdf - SRAM and EPROM mapped as ROM - 4/1987 page 26-34, plus corrections in 5/1987 page 32-34