Difference between revisions of "6502"

(→Opcode matrix including illegal opcodes) |

(→Opcode matrix including illegal opcodes) |

||

| Line 460: | Line 460: | ||

{| class="wikitable" style="white-space: nowrap;" | {| class="wikitable" style="white-space: nowrap;" | ||

|- | |- | ||

| − | |colspan= | + | |colspan=17| Addressing modes: <span style="background-color: #e0e0e0;">'''A''' - accumulator</span>, <span style="background-color: #e0ffe0;">'''#''' - immediate</span>, <span style="background-color: #ffe0e0;">'''zpg''' - zero page</span>, <span style="background-color: #e0ffff;">'''abs''' - absolute</span>, <span style="background-color: #ffe0ff;">'''ind''' - indirect</span>, <span style="background-color: #ffffe0;">'''rel''' - relative</span>. Uncolored cells are illegal opcodes. |

|- | |- | ||

!rowspan=2| High nibble ||colspan=16| Low nibble | !rowspan=2| High nibble ||colspan=16| Low nibble | ||

Revision as of 01:47, 3 September 2024

6502 info taken from Wikipedia.org

The MOS Technology 6502 is an 8-bit microprocessor designed by Chuck Peddle for MOS Technology in 1975. When it was introduced it was the least expensive full featured CPU on the market by far, at about 1/6th the price, or less, of competing designs from larger companies such as Motorola and Intel. It was nevertheless faster than most of them, and, along with the Zilog Z80, sparked off a series of computer projects that would eventually result in the home computer revolution of the 1980s. The 6502 design was originally second-sourced by Rockwell and Synertek and later licensed to a number of companies; it is still made for embedded systems.

The 6502 was used, among others, for Commodore's 8-bit machines.

Originally the CPC was destined to be designed around the 6502 processor. But when Amstrad approached Locomotive Software to develop a Basic for it with a very tight deadline, Locomotive PLC, who already had a Z80 Basic in the works, urged and convinced Amstrad to switch to the Z80.

Contents

Registers

| Register | Size | Description | Notes |

|---|---|---|---|

| A (Accumulator) | 8-bit | Main register for arithmetic, logic, and data transfer | Most operations use this register |

| X (Index Register X) | 8-bit | Used for indexing memory and loop counters | Can be used for addressing modes like Indexed Indirect, Zero Page Indexed, and Absolute Indexed |

| Y (Index Register Y) | 8-bit | Used for indexing memory and loop counters | Often used in Absolute and Zero Page Indexed addressing |

| P (Processor Status) | 8-bit |

|

The status register is modified by arithmetic and logic operations, as well as interrupts |

| S (Stack Pointer) | 8-bit | Points to the current location in the stack | Stack is located in page 1 ($0100-$01FF), 8-bit S is offset to this base |

| PC (Program Counter) | 16-bit | Points to the next instruction to be executed | Automatically increments as instructions are executed |

6502 Instruction set

Standard instructions

| Mnemonic | Operation | Addressing Modes | Flags | Description | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| No arg | A | #$nn | $nnnn | $nnnn,X | $nnnn,Y | ($nnnn) | $nn | $nn,X | $nn,Y | ($nn,X) | ($nn),Y | $nnnn | N | V | - | B | D | I | Z | C | |||

| ADC | A + M + C → A, C | 69 | 6D | 7D | 79 | 65 | 75 | 61 | 71 | N | V | - | - | - | - | Z | C | Add Memory to Accumulator with Carry | |||||

| AND | A ∧ M → A | 29 | 2D | 3D | 39 | 25 | 35 | 21 | 31 | N | - | - | - | - | - | Z | - | "AND" Memory with Accumulator | |||||

| ASL | C ← /M7...M0/ ← 0 | 0A | 0E | 1E | 06 | 16 | N | - | - | - | - | - | Z | C | Arithmetic Shift Left | ||||||||

| BCC | Branch on C = 0 | 90 | - | - | - | - | - | - | - | - | Branch on Carry Clear | ||||||||||||

| BCS | Branch on C = 1 | B0 | - | - | - | - | - | - | - | - | Branch on Carry Set | ||||||||||||

| BEQ | Branch on Z = 1 | F0 | - | - | - | - | - | - | - | - | Branch on Result Zero | ||||||||||||

| BIT | A ∧ M, M7 → N, M6 → V | 2C | 24 | N | V | - | - | - | - | Z | - | Test Bits in Memory with Accumulator | |||||||||||

| BMI | Branch on N = 1 | 30 | - | - | - | - | - | - | - | - | Branch on Result Minus | ||||||||||||

| BNE | Branch on Z = 0 | D0 | - | - | - | - | - | - | - | - | Branch on Result Not Zero | ||||||||||||

| BPL | Branch on N = 0 | 10 | - | - | - | - | - | - | - | - | Branch on Result Plus | ||||||||||||

| BRK | PC + 2↓, [FFFE] → PCL, [FFFF] → PCH | 00 | - | - | - | - | - | 1 | - | - | Break Command | ||||||||||||

| BVC | Branch on V = 0 | 50 | - | - | - | - | - | - | - | - | Branch on Overflow Clear | ||||||||||||

| BVS | Branch on V = 1 | 70 | - | - | - | - | - | - | - | - | Branch on Overflow Set | ||||||||||||

| CLC | 0 → C | 18 | - | - | - | - | - | - | - | 0 | Clear Carry Flag | ||||||||||||

| CLD | 0 → D | D8 | - | - | - | - | 0 | - | - | - | Clear Decimal Mode | ||||||||||||

| CLI | 0 → I | 58 | - | - | - | - | - | 0 | - | - | Clear Interrupt Disable | ||||||||||||

| CLV | 0 → V | B8 | - | 0 | - | - | - | - | - | - | Clear Overflow Flag | ||||||||||||

| CMP | A - M | C9 | CD | DD | D9 | C5 | D5 | C1 | D1 | N | - | - | - | - | - | Z | C | Compare Memory and Accumulator | |||||

| CPX | X - M | E0 | EC | E4 | N | - | - | - | - | - | Z | C | Compare Index Register X To Memory | ||||||||||

| CPY | Y - M | C0 | CC | C4 | N | - | - | - | - | - | Z | C | Compare Index Register Y To Memory | ||||||||||

| DEC | M - 1 → M | CE | DE | C6 | D6 | N | - | - | - | - | - | Z | - | Decrement Memory By One | |||||||||

| DEX | X - 1 → X | CA | N | - | - | - | - | - | Z | - | Decrement Index Register X By One | ||||||||||||

| DEY | Y - 1 → Y | 88 | N | - | - | - | - | - | Z | - | Decrement Index Register Y By One | ||||||||||||

| EOR | A ⊻ M → A | 49 | 4D | 5D | 59 | 45 | 55 | 41 | 51 | N | - | - | - | - | - | Z | - | "Exclusive OR" Memory with Accumulator | |||||

| INC | M + 1 → M | EE | FE | E6 | F6 | N | - | - | - | - | - | Z | - | Increment Memory By One | |||||||||

| INX | X + 1 → X | E8 | N | - | - | - | - | - | Z | - | Increment Index Register X By One | ||||||||||||

| INY | Y + 1 → Y | C8 | N | - | - | - | - | - | Z | - | Increment Index Register Y By One | ||||||||||||

| JMP | [PC + 1] → PCL, [PC + 2] → PCH | 4C | 6C | - | - | - | - | - | - | - | - | JMP Indirect | |||||||||||

| JSR | PC + 2↓, [PC + 1] → PCL, [PC + 2] → PCH | 20 | - | - | - | - | - | - | - | - | Jump To Subroutine | ||||||||||||

| LDA | M → A | A9 | AD | BD | B9 | A5 | B5 | A1 | B1 | N | - | - | - | - | - | Z | - | Load Accumulator with Memory | |||||

| LDX | M → X | A2 | AE | BE | A6 | B6 | N | - | - | - | - | - | Z | - | Load Index Register X From Memory | ||||||||

| LDY | M → Y | A0 | AC | BC | A4 | B4 | N | - | - | - | - | - | Z | - | Load Index Register Y From Memory | ||||||||

| LSR | 0 → /M7...M0/ → C | 4A | 4E | 5E | 46 | 56 | 0 | - | - | - | - | - | Z | C | Logical Shift Right | ||||||||

| NOP | No operation | EA | - | - | - | - | - | - | - | - | No Operation | ||||||||||||

| ORA | A ∨ M → A | 09 | 0D | 1D | 19 | 05 | 15 | 01 | 11 | N | - | - | - | - | - | Z | - | "OR" Memory with Accumulator | |||||

| PHA | A↓ | 48 | - | - | - | - | - | - | - | - | Push Accumulator On Stack | ||||||||||||

| PHP | P↓ | 08 | - | - | - | - | - | - | - | - | Push Processor Status On Stack | ||||||||||||

| PLA | A↑ | 68 | N | - | - | - | - | - | Z | - | Pull Accumulator From Stack | ||||||||||||

| PLP | P↑ | 28 | N | V | - | - | D | I | Z | C | Pull Processor Status From Stack | ||||||||||||

| ROL | C ← /M7...M0/ ← C | 2A | 2E | 3E | 26 | 36 | N | - | - | - | - | - | Z | C | Rotate Left | ||||||||

| ROR | C → /M7...M0/ → C | 6A | 6E | 7E | 66 | 76 | N | - | - | - | - | - | Z | C | Rotate Right | ||||||||

| RTI | P↑ PC↑ | 40 | N | V | - | - | D | I | Z | C | Return From Interrupt | ||||||||||||

| RTS | PC↑, PC + 1 → PC | 60 | - | - | - | - | - | - | - | - | Return From Subroutine | ||||||||||||

| SBC | A - M - ~C → A | E9 | ED | FD | F9 | E5 | F5 | E1 | F1 | N | V | - | - | - | - | Z | C | Subtract Memory from Accumulator with Borrow | |||||

| SEC | 1 → C | 38 | - | - | - | - | - | - | - | 1 | Set Carry Flag | ||||||||||||

| SED | 1 → D | F8 | - | - | - | - | 1 | - | - | - | Set Decimal Mode | ||||||||||||

| SEI | 1 → I | 78 | - | - | - | - | - | 1 | - | - | Set Interrupt Disable | ||||||||||||

| STA | A → M | 8D | 9D | 99 | 85 | 95 | 81 | 91 | - | - | - | - | - | - | - | - | Store Accumulator in Memory | ||||||

| STX | X → M | 8E | 86 | 96 | - | - | - | - | - | - | - | - | Store Index Register X In Memory | ||||||||||

| STY | Y → M | 8C | 84 | 94 | - | - | - | - | - | - | - | - | Store Index Register Y In Memory | ||||||||||

| TAX | A → X | AA | N | - | - | - | - | - | Z | - | Transfer Accumulator To Index X | ||||||||||||

| TAY | A → Y | A8 | N | - | - | - | - | - | Z | - | Transfer Accumulator To Index Y | ||||||||||||

| TSX | S → X | BA | N | - | - | - | - | - | Z | - | Transfer Stack Pointer To Index X | ||||||||||||

| TXA | X → A | 8A | N | - | - | - | - | - | Z | - | Transfer Index X To Accumulator | ||||||||||||

| TXS | X → S | 9A | - | - | - | - | - | - | - | - | Transfer Index X To Stack Pointer | ||||||||||||

| TYA | Y → A | 98 | N | - | - | - | - | - | Z | - | Transfer Index Y To Accumulator | ||||||||||||

Illegal instructions

| Mnemonic | Operation | Addressing Modes | Flags | Description | ||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| No arg | #$nn | $nnnn | $nnnn,X | $nnnn,Y | $nn | $nn,X | $nn,Y | ($nn,X) | ($nn),Y | N | V | - | B | D | I | Z | C | |||

| ANC | A ∧ M → A, N → C | 0B, 2B | N | - | - | - | - | - | Z | C | "AND" Memory with Accumulator then Move Negative Flag to Carry Flag | |||||||||

| ARR | (A ∧ M) / 2 → A | 6B | N | V | - | - | - | - | Z | C | "AND" Accumulator then Rotate Right | |||||||||

| ASR | (A ∧ M) / 2 → A | 4B | 0 | - | - | - | - | - | Z | C | "AND" then Logical Shift Right | |||||||||

| DCP | M - 1 → M, A - M | CF | DF | DB | C7 | D7 | C3 | D3 | N | - | - | - | - | - | Z | C | Decrement Memory By One then Compare with Accumulator | |||

| ISC | M + 1 → M, A - M → A | EF | FF | FB | E7 | F7 | E3 | F3 | N | V | - | - | - | - | Z | C | Increment Memory By One then SBC then Subtract Memory from Accumulator with Borrow | |||

| JAM | Stop execution | 02, 12, 22, 32, 42, 52, 62, 72, 92, B2, D2, F2 | - | - | - | - | - | - | - | - | Halt the CPU | |||||||||

| LAS | M ∧ S → A, X, S | BB | N | - | - | - | - | - | Z | - | "AND" Memory with Stack Pointer | |||||||||

| LAX | M → A, X | AB | AF | BF | A7 | B7 | A3 | B3 | N | - | - | - | - | - | Z | - | Load Accumulator and Index Register X From Memory | |||

| NOP | No operation | 1A, 3A, 5A, 7A, DA, FA | 80, 82, 89, C2, E2 | 0C | 1C, 3C, 5C, 7C, DC, FC | 04, 44, 64 | 14, 34, 54, 74, D4, F4 | - | - | - | - | - | - | - | - | No Operation | ||||

| RLA | C ← /M7...M0/ ← C, A ∧ M → A | 2F | 3F | 3B | 27 | 37 | 23 | 33 | N | - | - | - | - | - | Z | C | Rotate Left then "AND" with Accumulator | |||

| RRA | C → /M7...M0/ → C, A + M + C → A | 6F | 7F | 7B | 67 | 77 | 63 | 73 | N | V | - | - | - | - | Z | C | Rotate Right and Add Memory to Accumulator | |||

| SAX | A ∧ X → M | 8F | 87 | 97 | 83 | - | - | - | - | - | - | - | - | Store Accumulator "AND" Index Register X in Memory | ||||||

| SBC | A - M - ~C → A | EB | N | V | - | - | - | - | Z | C | Subtract Memory from Accumulator with Borrow | |||||||||

| SBX | (A ∧ X) - M → X | CB | N | - | - | - | - | - | Z | C | Subtract Memory from Accumulator "AND" Index Register X | |||||||||

| SHA | A ∧ X ∧ V → M | 9F | 93 | - | - | - | - | - | - | - | - | Store Accumulator "AND" Index Register X "AND" Value | ||||||||

| SHS | A ∧ X → S, S ∧ (H + 1) → M | 9B | - | - | - | - | - | - | - | - | Transfer Accumulator "AND" Index Register X to Stack Pointer then Store Stack Pointer "AND" Hi-Byte In Memory | |||||||||

| SHX | X ∧ (H + 1) → M | 9E | - | - | - | - | - | - | - | - | Store Index Register X "AND" Value | |||||||||

| SHY | Y ∧ (H + 1) → M | 9C | - | - | - | - | - | - | - | - | Store Index Register Y "AND" Value | |||||||||

| SLO | M * 2 → M, A ∨ M → A | 0F | 1F | 1B | 07 | 17 | 03 | 13 | N | - | - | - | - | - | Z | C | Arithmetic Shift Left then "OR" Memory with Accumulator | |||

| SRE | M / 2 → M, A ⊻ M → A | 4F | 5F | 5B | 47 | 57 | 43 | 53 | N | - | - | - | - | - | Z | C | Logical Shift Right then "Exclusive OR" Memory with Accumulator | |||

| XAA | (A ∨ V) ∧ X ∧ M → A | 8B | N | - | - | - | - | - | Z | - | Non-deterministic Operation of Accumulator, Index Register X, Memory and Bus Contents | |||||||||

Official opcode matrix

| Addressing modes: A - accumulator, # - immediate, zpg - zero page, abs - absolute, ind - indirect, X - indexed by X register, Y - indexed by Y register, rel - relative | ||||||||||||

| High nibble | Low nibble | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 2 | 4 | 5 | 6 | 8 | 9 | A | C | D | E | |

| 0 | BRK | ORA (ind,X) | ORA zpg | ASL zpg | PHP | ORA # | ASL A | ORA abs | ASL abs | |||

| 1 | BPL rel | ORA (ind),Y | ORA zpg,X | ASL zpg,X | CLC | ORA abs,Y | ORA abs,X | ASL abs,X | ||||

| 2 | JSR abs | AND (ind,X) | BIT zpg | AND zpg | ROL zpg | PLP | AND # | ROL A | BIT abs | AND abs | ROL abs | |

| 3 | BMI rel | AND (ind),Y | AND zpg,X | ROL zpg,X | SEC | AND abs,Y | AND abs,X | ROL abs,X | ||||

| 4 | RTI | EOR (ind,X) | EOR zpg | LSR zpg | PHA | EOR # | LSR A | JMP abs | EOR abs | LSR abs | ||

| 5 | BVC rel | EOR (ind),Y | EOR zpg,X | LSR zpg,X | CLI | EOR abs,Y | EOR abs,X | LSR abs,X | ||||

| 6 | RTS | ADC (ind,X) | ADC zpg | ROR zpg | PLA | ADC # | ROR A | JMP (ind) | ADC abs | ROR abs | ||

| 7 | BVS rel | ADC (ind),Y | ADC zpg,X | ROR zpg,X | SEI | ADC abs,Y | ADC abs,X | ROR abs,X | ||||

| 8 | STA (ind,X) | STY zpg | STA zpg | STX zpg | DEY | TXA | STY abs | STA abs | STX abs | |||

| 9 | BCC rel | STA (ind),Y | STY zpg,X | STA zpg,X | STX zpg,Y | TYA | STA abs,Y | TXS | STA abs,X | |||

| A | LDY # | LDA (ind,X) | LDX # | LDY zpg | LDA zpg | LDX zpg | TAY | LDA # | TAX | LDY abs | LDA abs | LDX abs |

| B | BCS rel | LDA (ind),Y | LDY zpg,X | LDA zpg,X | LDX zpg,Y | CLV | LDA abs,Y | TSX | LDY abs,X | LDA abs,X | LDX abs,Y | |

| C | CPY # | CMP (ind,X) | CPY zpg | CMP zpg | DEC zpg | INY | CMP # | DEX | CPY abs | CMP abs | DEC abs | |

| D | BNE rel | CMP (ind),Y | CMP zpg,X | DEC zpg,X | CLD | CMP abs,Y | CMP abs,X | DEC abs,X | ||||

| E | CPX # | SBC (ind,X) | CPX zpg | SBC zpg | INC zpg | INX | SBC # | NOP | CPX abs | SBC abs | INC abs | |

| F | BEQ rel | SBC (ind),Y | SBC zpg,X | INC zpg,X | SED | SBC abs,Y | SBC abs,X | INC abs,X | ||||

| Blank opcodes (e.g., F2) and all opcodes whose low nibbles are 3, 7, B and F are undefined in the official 6502 instruction set. | ||||||||||||

Opcode matrix including illegal opcodes

| Addressing modes: A - accumulator, # - immediate, zpg - zero page, abs - absolute, ind - indirect, rel - relative. Uncolored cells are illegal opcodes. | ||||||||||||||||

| High nibble | Low nibble | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F | |

| 0 | BRK | ORA (ind,X) | JAM | SLO (ind,X) | NOP zpg | ORA zpg | ASL zpg | SLO zpg | PHP | ORA # | ASL A | ANC # | NOP abs | ORA abs | ASL abs | SLO abs |

| 1 | BPL rel | ORA (ind),Y | JAM | SLO (ind),Y | NOP zpg,X | ORA zpg,X | ASL zpg,X | SLO zpg,X | CLC | ORA abs,Y | NOP | SLO abs,Y | NOP abs,X | ORA abs,X | ASL abs,X | SLO abs,X |

| 2 | JSR abs | AND (ind,X) | JAM | RLA (ind,X) | BIT zpg | AND zpg | ROL zpg | RLA zpg | PLP | AND # | ROL A | ANC # | BIT abs | AND abs | ROL abs | RLA abs |

| 3 | BMI rel | AND (ind),Y | JAM | RLA (ind),Y | NOP zpg,X | AND zpg,X | ROL zpg,X | RLA zpg,X | SEC | AND abs,Y | NOP | RLA abs,Y | NOP abs,X | AND abs,X | ROL abs,X | RLA abs,X |

| 4 | RTI | EOR (ind,X) | JAM | SRE (ind,X) | NOP zpg | EOR zpg | LSR zpg | SRE zpg | PHA | EOR # | LSR A | ALR # | JMP abs | EOR abs | LSR abs | SRE abs |

| 5 | BVC rel | EOR (ind),Y | JAM | SRE (ind),Y | NOP zpg,X | EOR zpg,X | LSR zpg,X | SRE zpg,X | CLI | EOR abs,Y | NOP | SRE abs,Y | NOP abs,X | EOR abs,X | LSR abs,X | SRE abs,X |

| 6 | RTS | ADC (ind,X) | JAM | RRA (ind,X) | NOP zpg | ADC zpg | ROR zpg | RRA zpg | PLA | ADC # | ROR A | ARR # | JMP (ind) | ADC abs | ROR abs | RRA abs |

| 7 | BVS rel | ADC (ind),Y | JAM | RRA (ind),Y | NOP zpg,X | ADC zpg,X | ROR zpg,X | RRA zpg,X | SEI | ADC abs,Y | NOP | RRA abs,Y | NOP abs,X | ADC abs,X | ROR abs,X | RRA abs,X |

| 8 | NOP # | STA (ind,X) | NOP # | SAX (ind,X) | STY zpg | STA zpg | STX zpg | SAX zpg | DEY | NOP # | TXA | ANE # | STY abs | STA abs | STX abs | SAX abs |

| 9 | BCC rel | STA (ind),Y | JAM | SHA (ind),Y | STY zpg,X | STA zpg,X | STX zpg,Y | SAX zpg,Y | TYA | STA abs,Y | TXS | TAS abs,Y | SHY abs,X | STA abs,X | SHX abs,Y | SHA abs,Y |

| A | LDY # | LDA (ind,X) | LDX # | LAX (ind,X) | LDY zpg | LDA zpg | LDX zpg | LAX zpg | TAY | LDA # | TAX | LXA # | LDY abs | LDA abs | LDX abs | LAX abs |

| B | BCS rel | LDA (ind),Y | JAM | LAX (ind),Y | LDY zpg,X | LDA zpg,X | LDX zpg,Y | LAX zpg,Y | CLV | LDA abs,Y | TSX | LAS abs,Y | LDY abs,X | LDA abs,X | LDX abs,Y | LAX abs,Y |

| C | CPY # | CMP (ind,X) | NOP # | DCP (ind,X) | CPY zpg | CMP zpg | DEC zpg | DCP zpg | INY | CMP # | DEX | AXS # | CPY abs | CMP abs | DEC abs | DCP abs |

| D | BNE rel | CMP (ind),Y | JAM | DCP (ind),Y | NOP zpg,X | CMP zpg,X | DEC zpg,X | DCP zpg,X | CLD | CMP abs,Y | NOP | DCP abs,Y | NOP abs,X | CMP abs,X | DEC abs,X | DCP abs,X |

| E | CPX # | SBC (ind,X) | NOP # | ISC (ind,X) | CPX zpg | SBC zpg | INC zpg | ISC zpg | INX | SBC # | NOP | SBC # | CPX abs | SBC abs | INC abs | ISC abs |

| F | BEQ rel | SBC (ind),Y | JAM | ISC (ind),Y | NOP zpg,X | SBC zpg,X | INC zpg,X | ISC zpg,X | SED | SBC abs,Y | NOP | ISC abs,Y | NOP abs,X | SBC abs,X | INC abs,X | ISC abs,X |

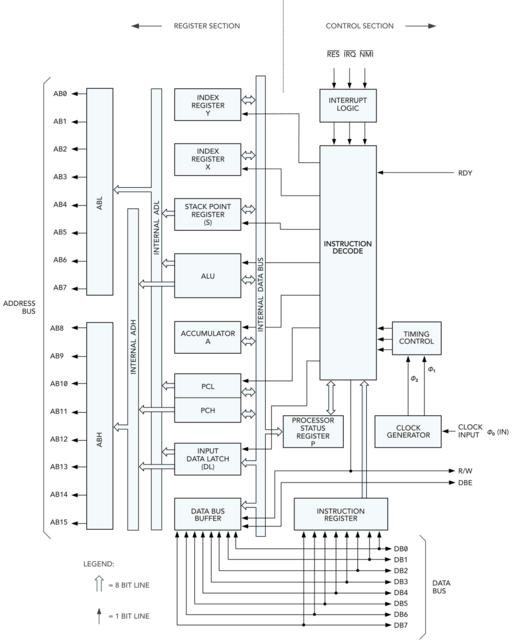

Block Diagram